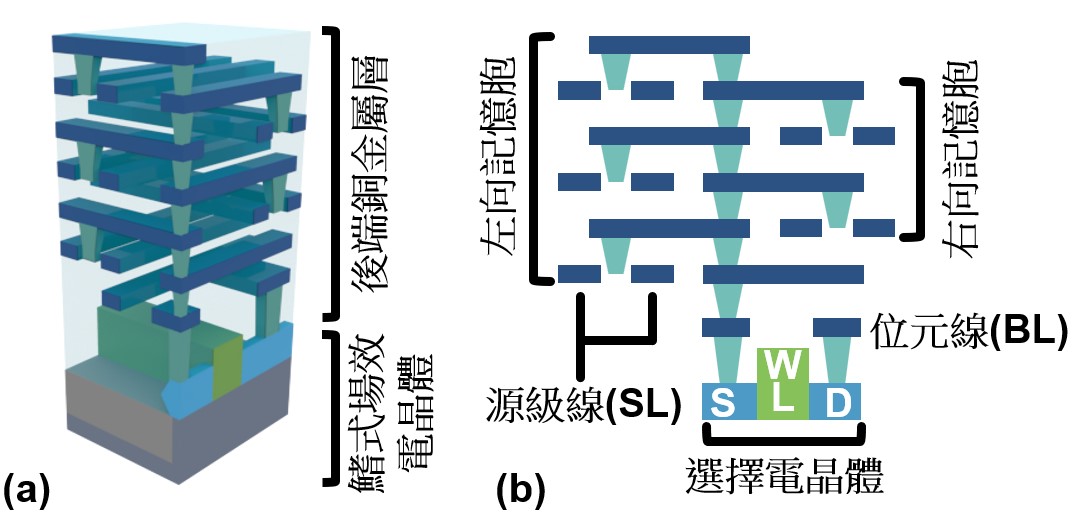

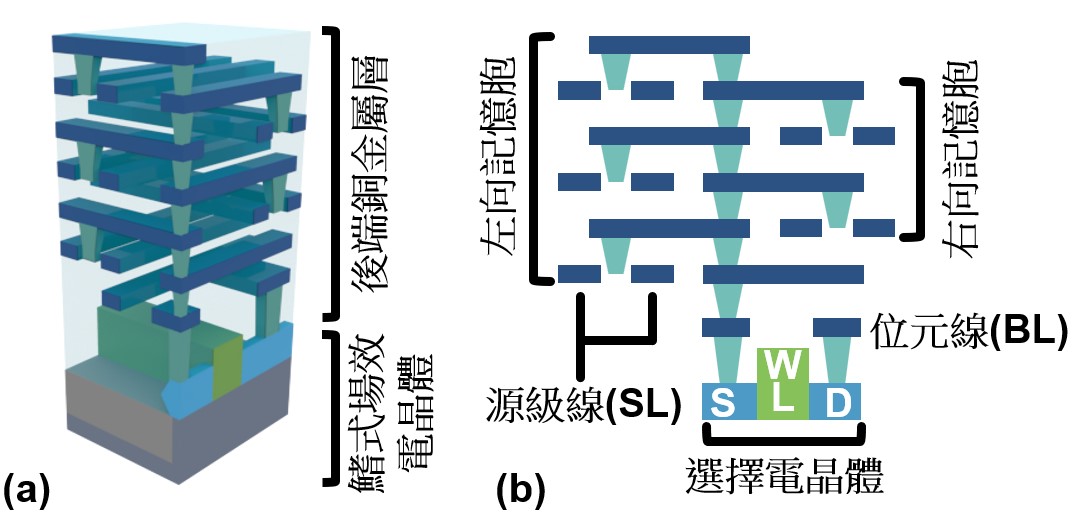

Introducing a groundbreaking high-density 3D Via Resistive Random Access Memory (RRAM) architecture seamlessly compatible with Fin Field-Effect Transistors (FinFETs) in logic processes. Through the careful design of a structure where vias and metal wires remain intentionally isolated in the layout, a Via RRAM is ingeniously crafted. This approach offers exceptional stackability, permitting each metal wire layer within the memory unit to incorporate a pair of RRAM elements, culminating in the creation of a remarkably high-density stackable embedded memory solution.

學研單位

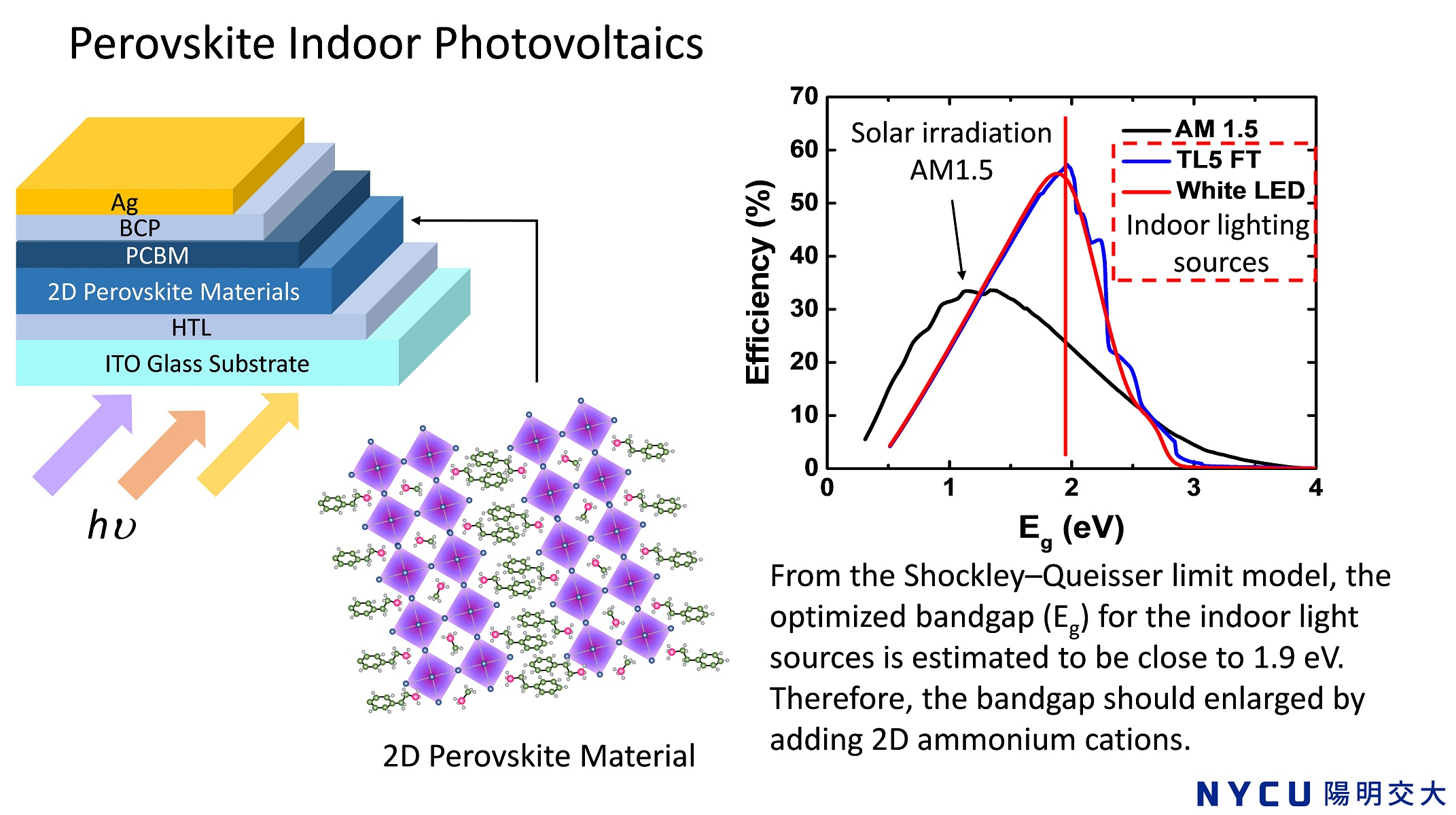

Emerging Two-Dimensional Perovskite Indoor Photovoltaics for Children Healthcare System Based on Internet of Things Technologies

Application of electrical responsive graphene-PVDF membrane in smart sensing clothing and sea-wave power generation

High-Toughness Structural Composite Designs by Artificial Intelligence and Bio-Materials Genome Initiative Platform

Integrated Rapid-Sensing Platform of Floating-Typed Magnetic SERS Substrate and Portable Raman Spectroscopy

Technology maturity:Experiment stage

Exhibiting purpose:Display of scientific results

Trading preferences:Negotiate by self

Coming soon!