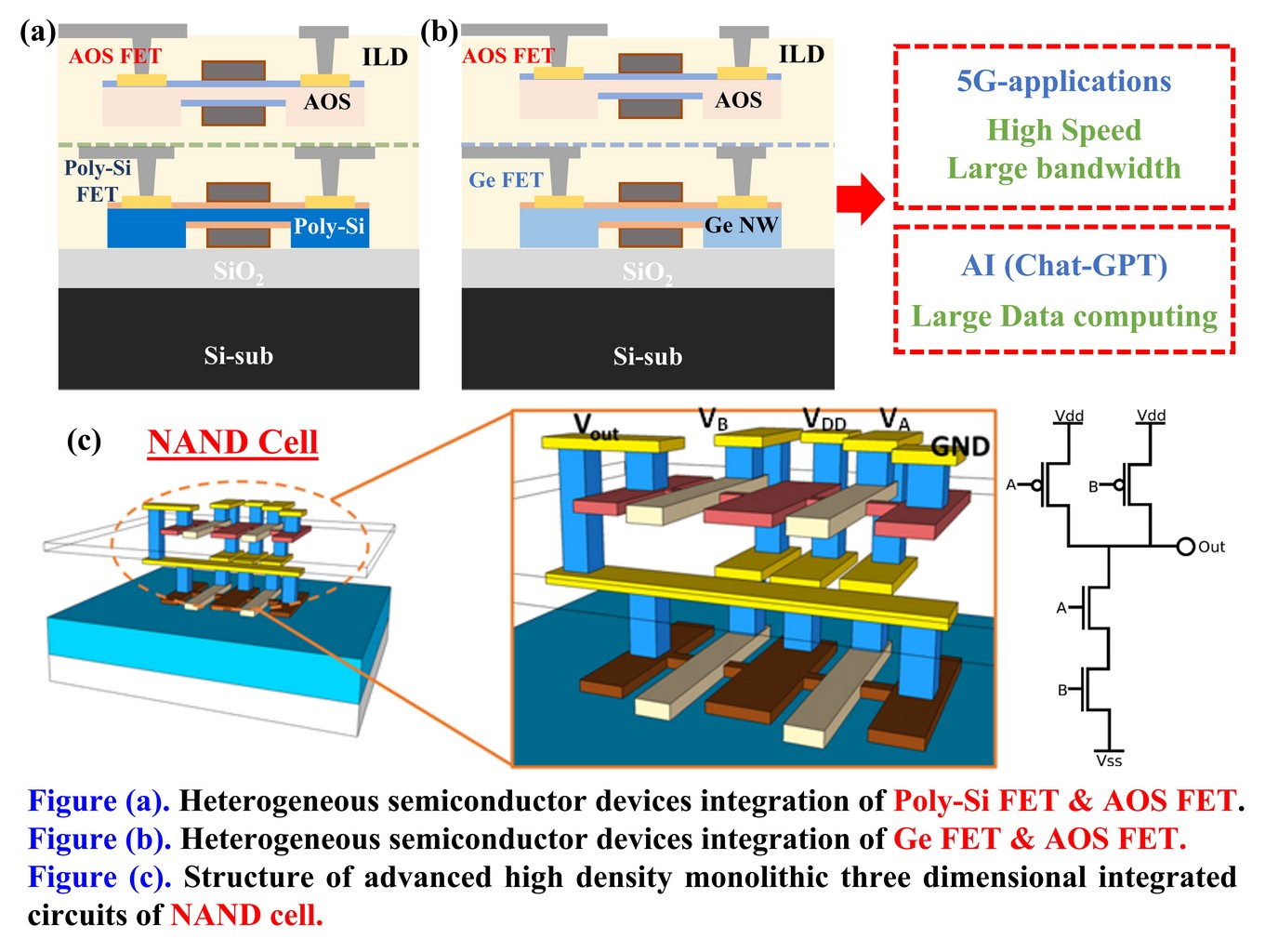

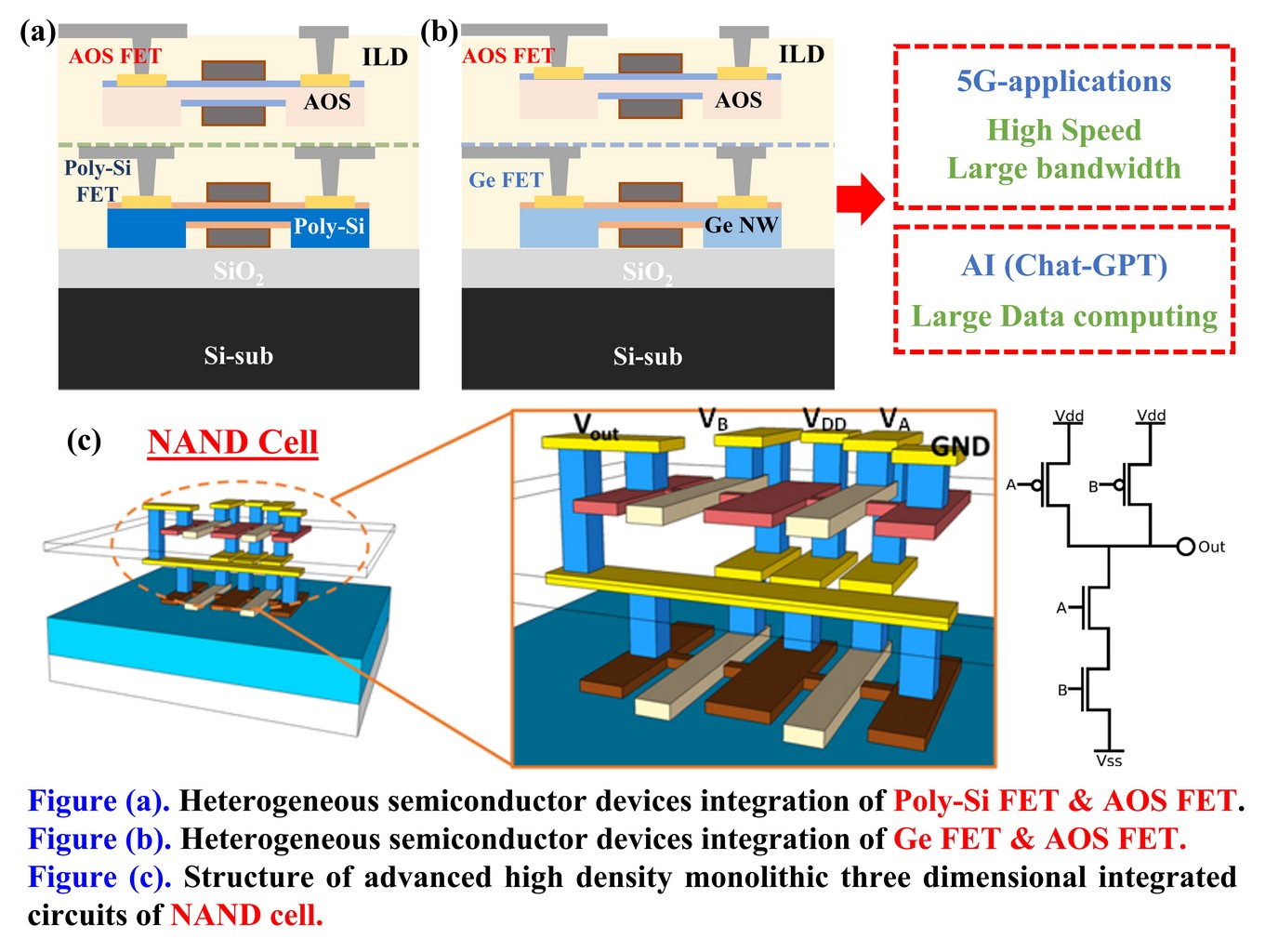

隨著半導體科技進步,新穎半導體材料與元件結構持續推陳出新,用以超越摩爾

定律之限制。藉由垂直式電路整合的方式發展三維積體電路是半導體科技進入到

埃米(Angstrom)世代的關鍵技術。單晶片三維積體電路(Monolithic 3D ICs, M3

D-ICs)技術是採用後段製程(BEOL)製作多層元件與電路層,並將其直接堆疊於前

段製程(FEOL)之電晶體元件層上方,因此M3D-ICs 技術具有更細短的垂直引洞連

接導線,可使電路佈局更加靈活、功率耗損更低。有鑑於此,本技術即在發展前

瞻異質半導體元件整合之單晶片三維堆疊超高密度邏輯閘積體電路技術。整體發

展架構可分為異質半導體組成的高效能電晶體元件技術、各異質元件層整合,以

及多層金屬連線佈局開發,最終以達成世界級紀錄的三維堆疊式超高密度反及閘

電路之實現為目標(~20M NAND-Gate/mm^2)。技術開發內容從新穎半導體體材料、高效能電晶體元件研製、製程技術整合,乃至邏輯閘電路實現等面向皆完整涵蓋。在此三維異質半導體元件整合架構中,將發展兩類型組合的前瞻元件整合技術,分別是先以閘極環繞式(Gate-all-around, GAA)單晶鍺基奈米薄片電晶體與複晶矽薄膜電晶體元件做為第一層高效能電晶體;接續,開發具有低製程熱預算的氧化物半導體,建置高效能閘極環繞式氧化銦基奈米薄片電晶體(GAA InOx-basednanosheet TFT),並將其堆疊於第一層的兩類型半導體元件層上方,做為第二層低功耗電晶體元件層,以有效提高單晶片中電晶體元件的積集度。本技術研發重點在於將第一層與第二層所研製的高效能異質半導體元件成功堆疊整合,並且解決異質半導體元件層間的堆疊佈局設計以及金屬連線技術問題,藉此實現超高密度邏輯閘陣列目標,即在1mm^2晶片面積內形成20 million (M)數量的反及閘(NAND)邏輯電路。由於一個NAND單元包含2顆n-channel FETs及2顆 p-channel FETs,所以一個20M NAND 邏輯閘陣列將含有高達80M顆電晶體,此外還需包含電晶體間之訊號連接線,且須於1 mm^2面積內實現。目前國際半導體大廠或國際知名學研機構尚無以三維堆疊方式實現此極高密度邏輯閘陣列之研發實例與成果,因此,本團隊所發展的異質半導體整合技術極具前瞻性與挑戰性,未來可展現延續摩爾定律的技術潛力。

國立陽明交通大學(NYCU)於2021年由國立陽明大學與國立交通大學合併而成,位於新竹市。學校擁有強大的科技、工程、醫學及社會科學領域,並在資訊技術、生物醫學、人工智慧等領域具有卓越的研究實力。國立陽明交通大學致力於跨領域合作與創新,並培養具全球視野的專業人才,積極應對社會挑戰與推動科技發展,為學術界和產業界作出重要貢獻。

技術成熟度:概念

展示目的:研發成果展示

流通方式:自行洽談

*服務單位

*姓名

*電話

*您參觀這項展品的主要目的?

*您是否希望進一步洽談

*您的職務類別

*展覽整體評價

*最喜歡的展區

*期待展覽著重的技術領域

*是否願意收到電子報/最新資訊

其他建議

敬請期待!