未來科技館

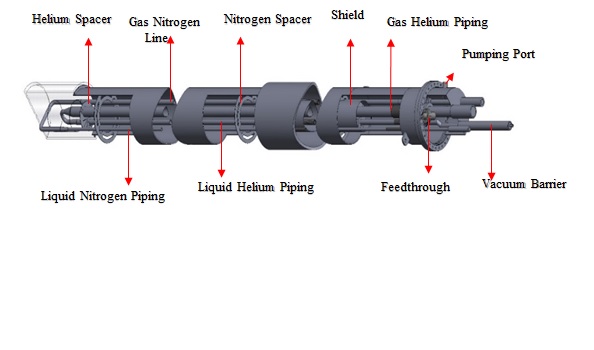

多內管型超低溫流體輸送管路專為液態和氣態氦、氮的傳輸而設計,旨在降低熱損。關鍵技術包括高效Spacer設計、真空絕熱和熱輻射隔絶,實測驗証每米管路熱損僅0.045 W,模擬結果為0.035 W,展現在液氦傳輸中的卓越性能和可靠性。

未來科技館 | 電子與光電

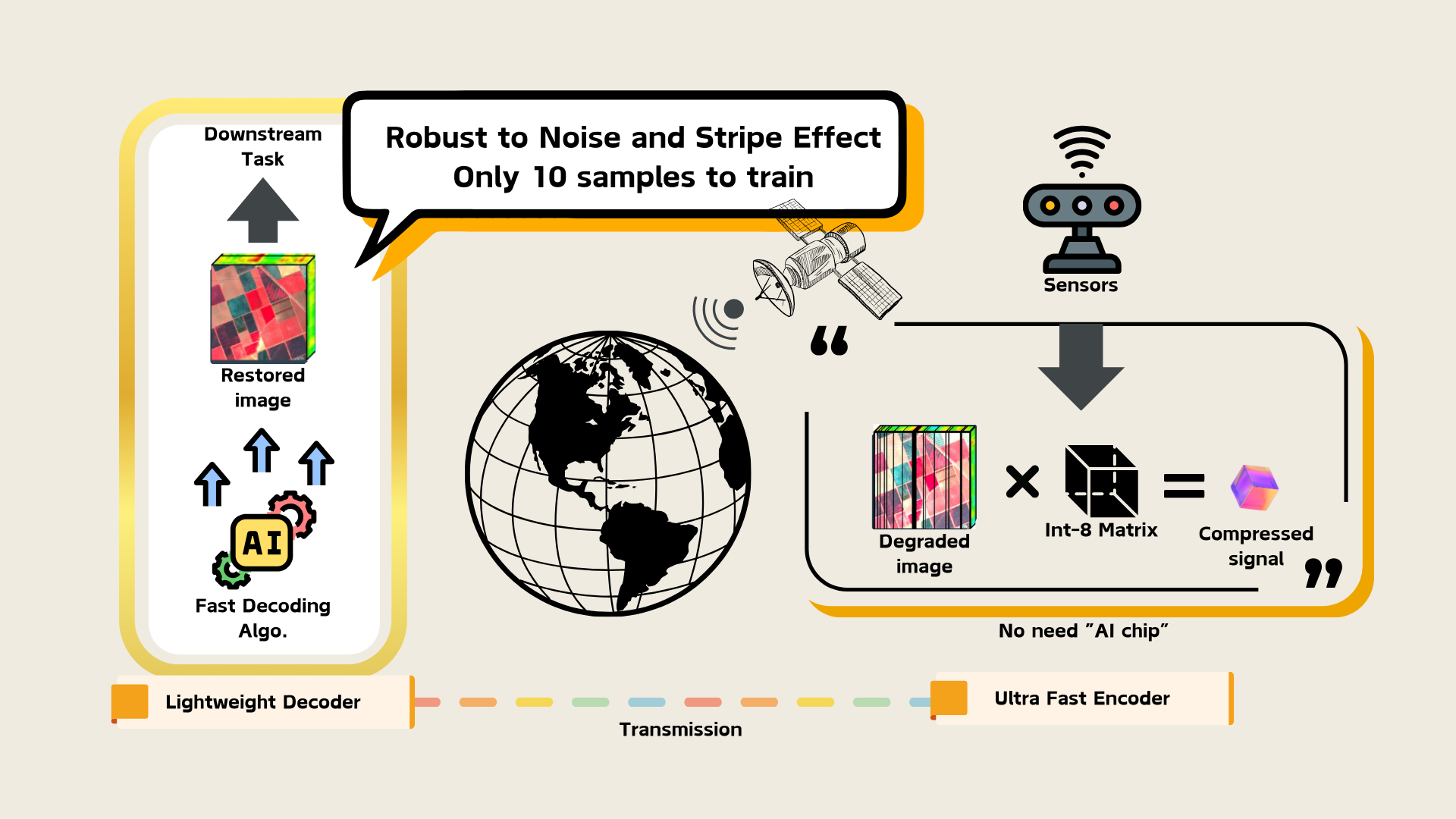

本研究開發創新的高光譜衛星影像感知、融合及安全傳輸技術,結合多光譜與高光譜影像優勢,提升空間頻譜解析度,並整合偽造影像辨識機制保護安全,技術並在 IEEE TGRS等頂尖期刊發表。此技術不僅提高了影像傳輸效率,還能確保影像真實性,具廣泛的市場應用潛力及顯著的經濟效益,推動產學合作及創新模式的建立。

未來科技館 | 資訊與通訊

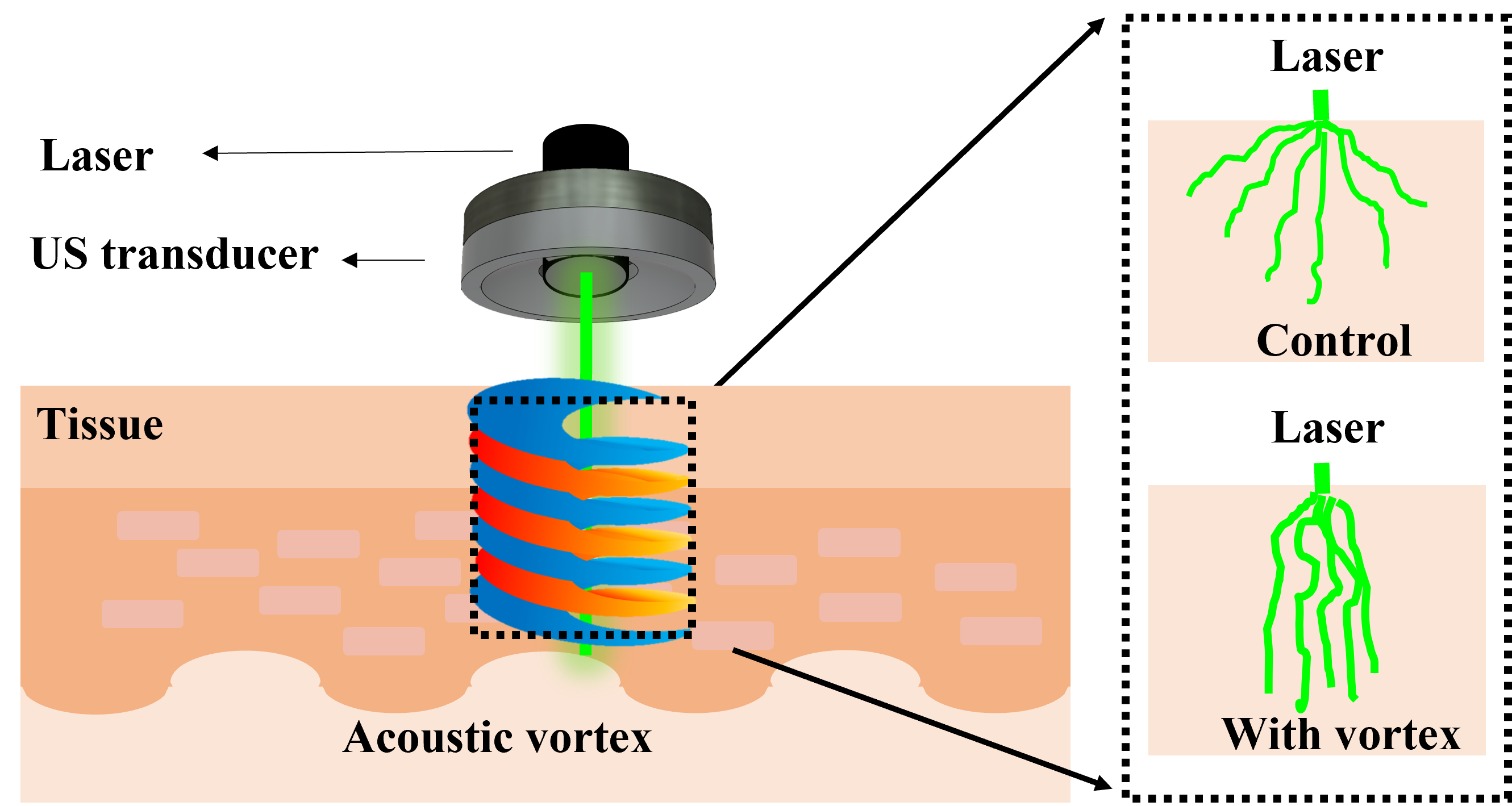

「漩渦式超音波光導技術」利用超音波在光傳遞路徑上形成的氣泡通道結構,能夠非接觸式、可動態調控、可逆且減緩光散射。本技術以聲渦流作為新型光導,使超音波形成特殊結構,大幅減少光在組織中的散射,光通量增加約34.3%。此技術操作簡單,非侵入式且降低組織損傷風險,為生物光學診斷治療帶來新解決方案。

未來科技館 | 電子與光電

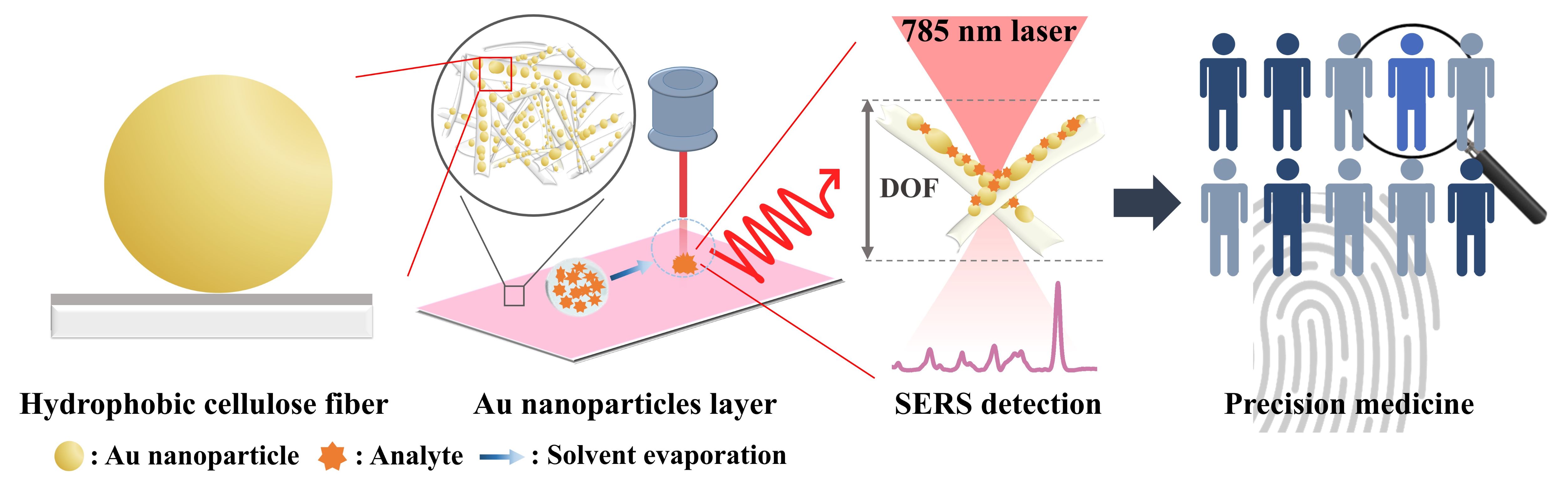

本團隊開發一種超高靈敏的分子指紋檢測平台,不僅搭配低成本的可攜式光譜儀即可展現單分子級的免標記檢測能力,同時兼具可量產、輕量、再現性佳、低背景螢光等特性,並成功與長庚醫院、馬偕醫院攜手進行臨床驗證,未來可應用於食品安全、臨床診斷與精準醫療所需快篩技術等重要民生相關議題,以提升國民健康與醫療品質。

未來科技館 | 生技與醫療敬請期待!