Key enabling light source technology for silicon photonics: Group-IV laser s monolithically integrated on silicon

Silicon photonics (SiPh) is an important technology in the fields of semico

nductor and optoelectronics. By manufacturing SiPh chips in modern CM

OS foundries, the powerful, cost-effective, and functional SiPh chips could

have a wide range of applications including optical communications, bio-

medical detection, and quantum-computing. However, the current bottle

neck of SiPh is the lack of efficient on-chip lasers due to the indirect-band

gap nature of group-IV semiconductors, limiting the further development

of SiPh. Thus, it is extremely to break the fundamental limitation to create

on-chip SiPh lasers.

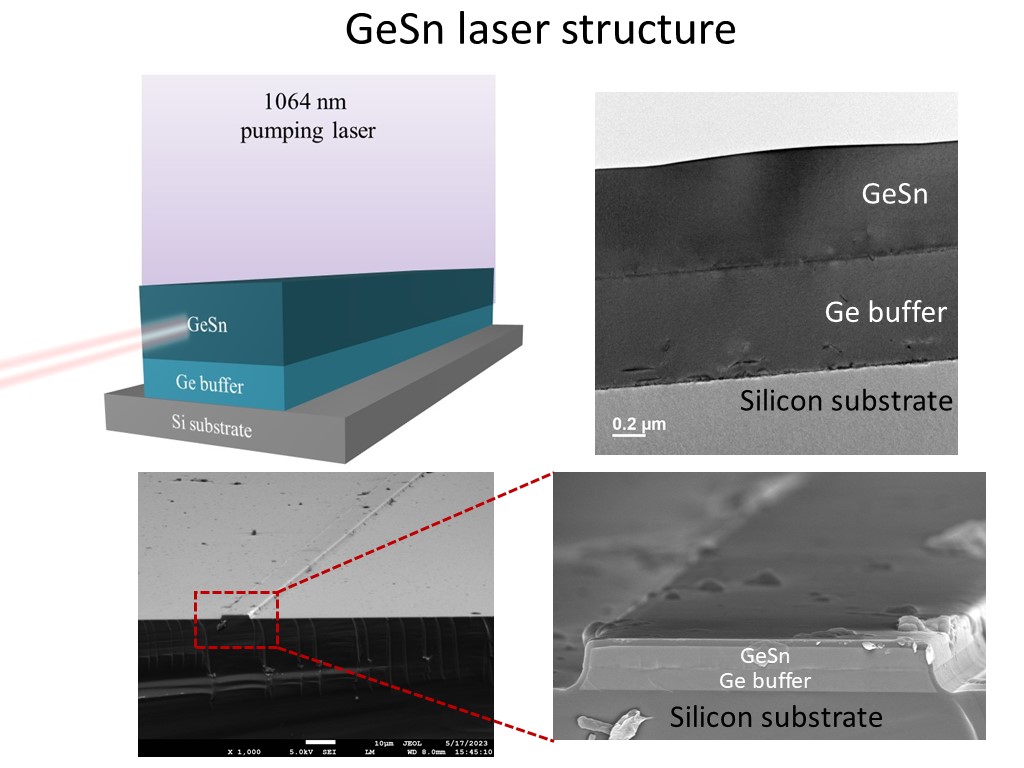

Here we demonstrate CMOS-compatible, monolithically-integrated group

-IV lasers on silicon as the important on-chip lasers for silicon photonics.

Using low-temperature growth technique and Ge buffer layer technique,

we successfully grew high-Sn-contnet GeSn layers with a direct bandgap

on silicon substrates. By processing the grown sample into laser cavities,

we achieved lasing action under optical pumping. The threshold of our Ge

Sn lasers is relative lower compared to the results from other group in the

world, and is comparable with III-V lasers. With the CMOS-compatibility, t

his technology could be used as the on-chip laser light sources for SiPh, e

nabling stronger and functional SiPh chips for a wide range of application

s.

National Chung Cheng University is a national university in Minxiong Township, Chiayi County, Taiwan. CCU is a member of the Association to Advance Collegiate Schools of Business.

Name:

Phone:

Address:No.168, Sec. 1, University Rd., Minhsiung Township, Chiayi County 621, Taiwan (R.O.C.)

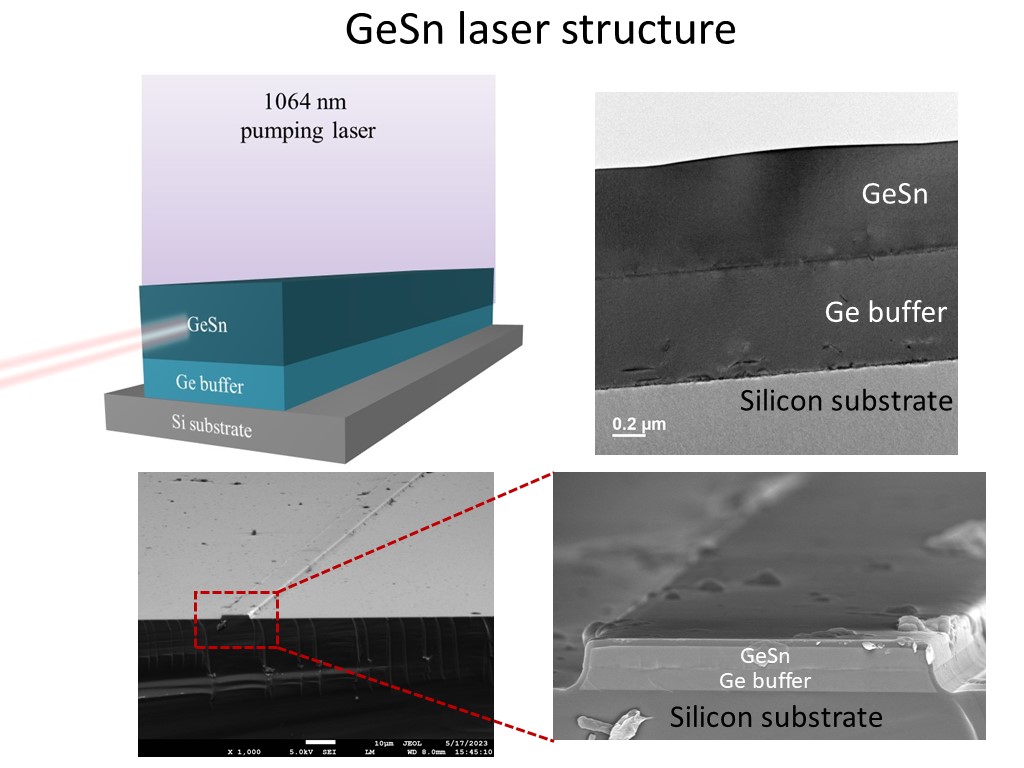

Multi-function silicon photonics integrated circuit for driving three-axis fi ber optic gyroscope

The innovative technology that turns waste into treasure – Silicon Dioxide regenerated from semiconductor waste that contains Silicon

Hybrid CMOS Inverter Comprised of Thin Film Transistors with Hetero-channel for Monolithic 3D-ICs and Ultra-high Resolution Flat-Panel Displays Applications

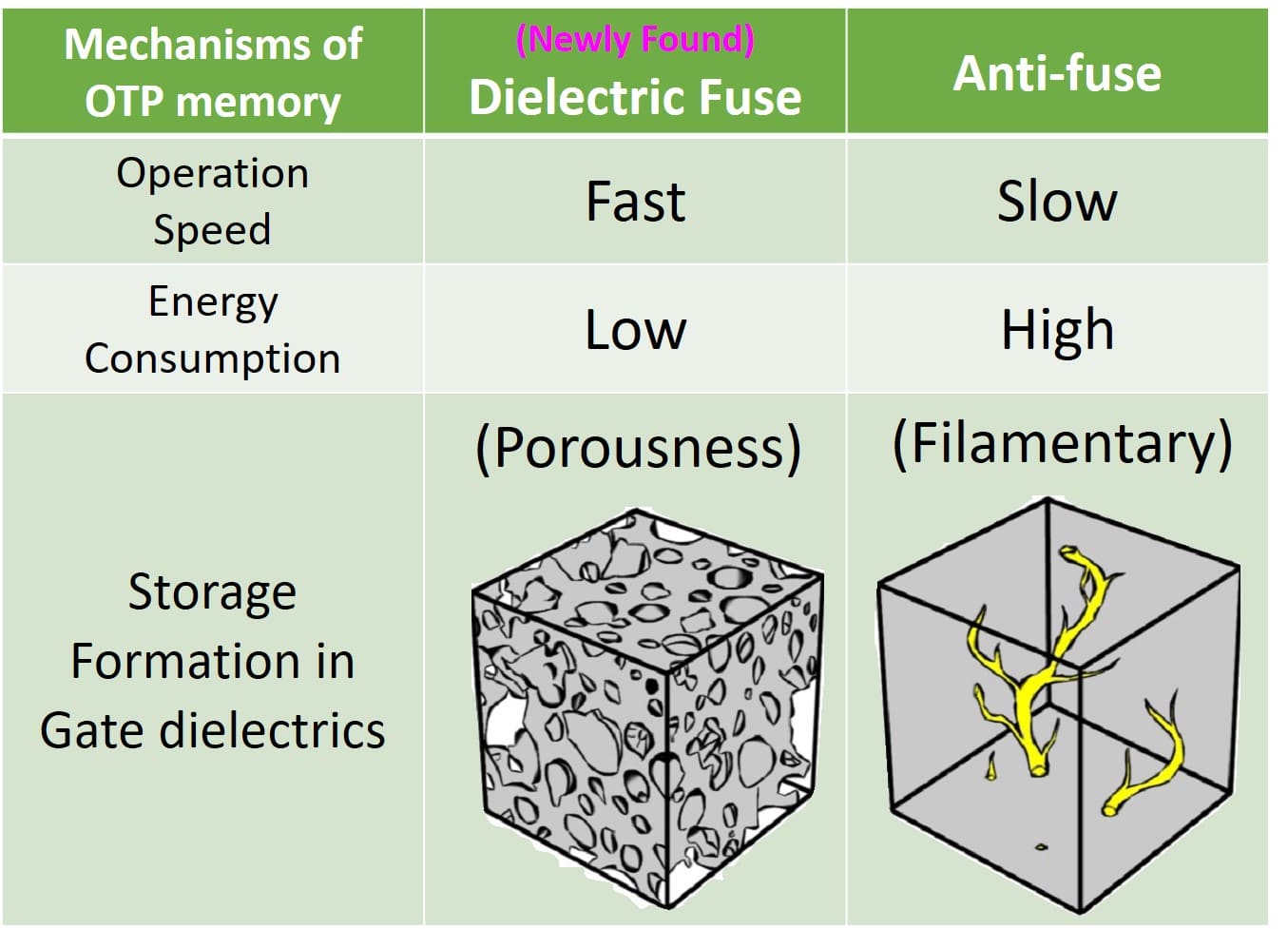

A Low-cost, Low-power, and High-speed “Dielectric-fuse Breakdown OTP” (dFuse OTP) Fully Integrated on CMOS Platform without Additional Masks

Technology maturity:Experiment stage

Exhibiting purpose:Display of scientific results

Trading preferences:Negotiate by self

*Organization

*Name

*Phone

*Main Purpose

*Discuss Further

*Job Category

*Overall Rating

*Favorite Area

*Key Tech Focus

*Willing to Receive Updates?

Other Suggestions

Coming soon!