AI accelerator chip architectural static performance analysis technology

The DNN network model is becoming more and more complex. To design an appropriate AI chip accelerator architecture to operate, it is necessary to find a balance between performance, power consumption, and cost, which increases design challenges. This innovative AI acceleration chip architecture analysis technology helps Industry players conduct architecture exploration, analysis, and design optimization in advance to help IC chip design house to enter the field of AI.

測試

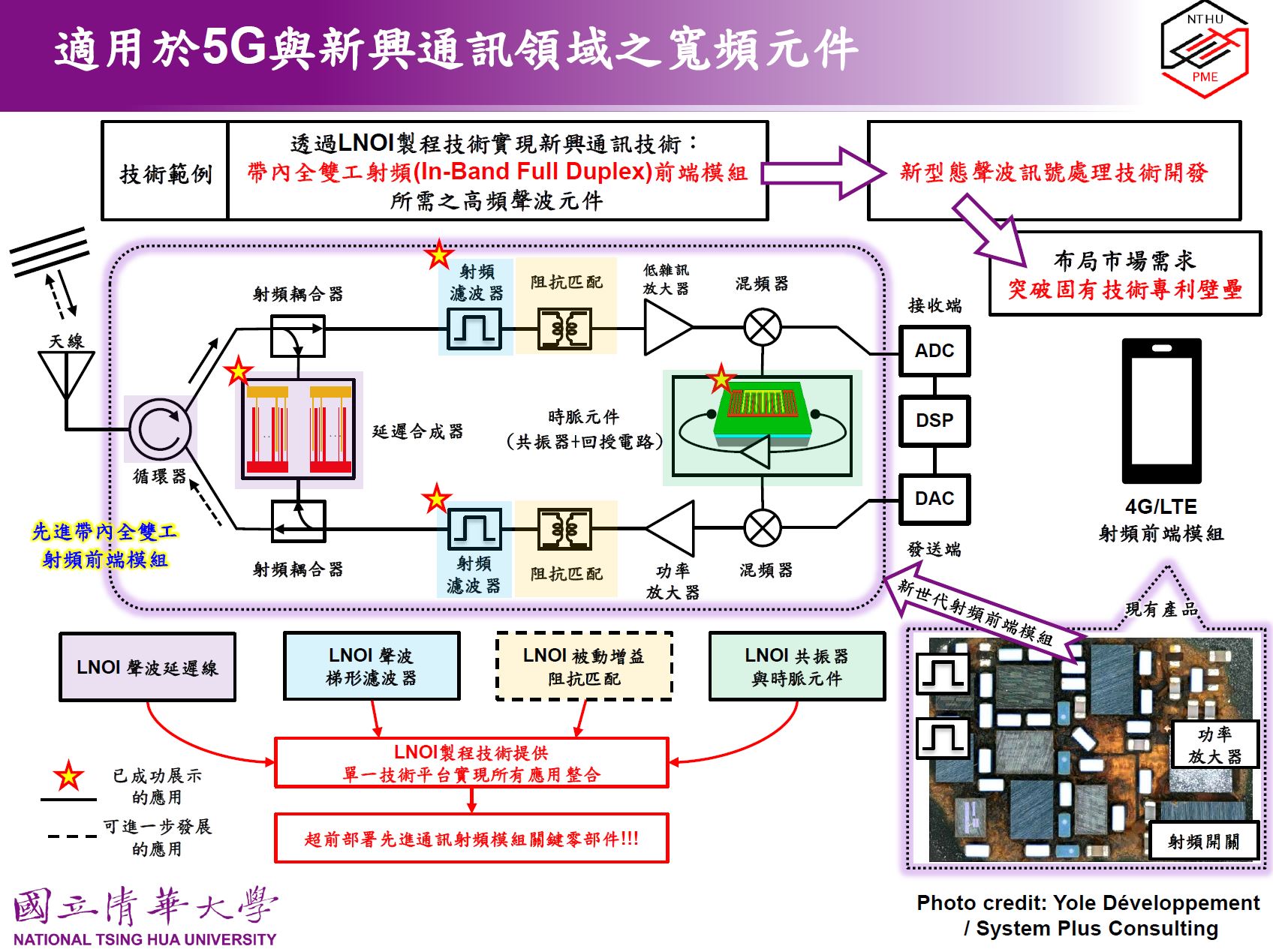

Next-generation wideband surface acoustic wave communication components based on thin-film lithium niobate on insulator technology

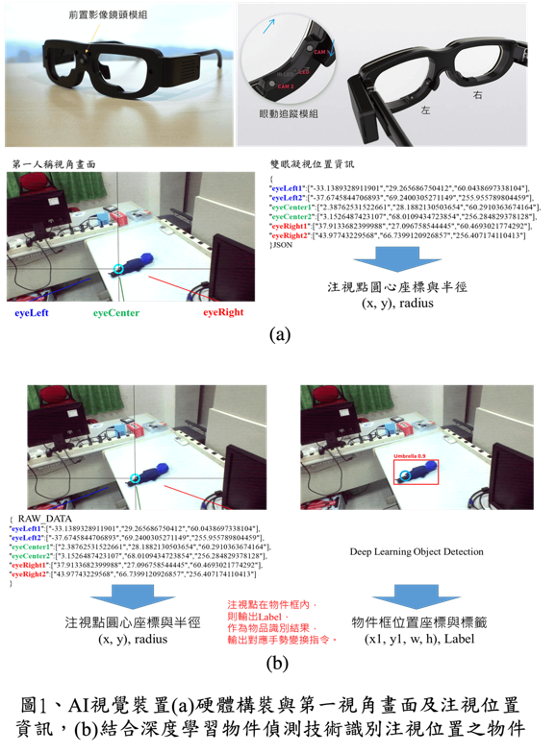

3D Printed Prosthetic Arm using Eye-Tracking and Artificial Intelligence Visual Recognition Technology

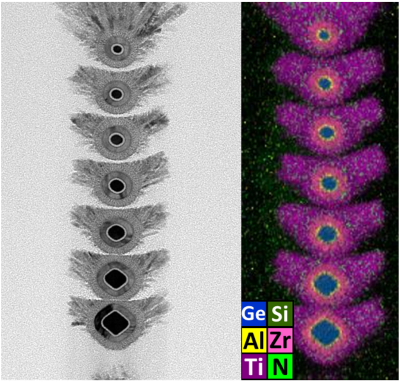

High mobility materials, process, stacked channels, and thermal circuit simulation; Ferroelectric X:HfO2 for Negative Capacitance and POC(Proof-of-Concept) Applications; Atomic layer technologies for

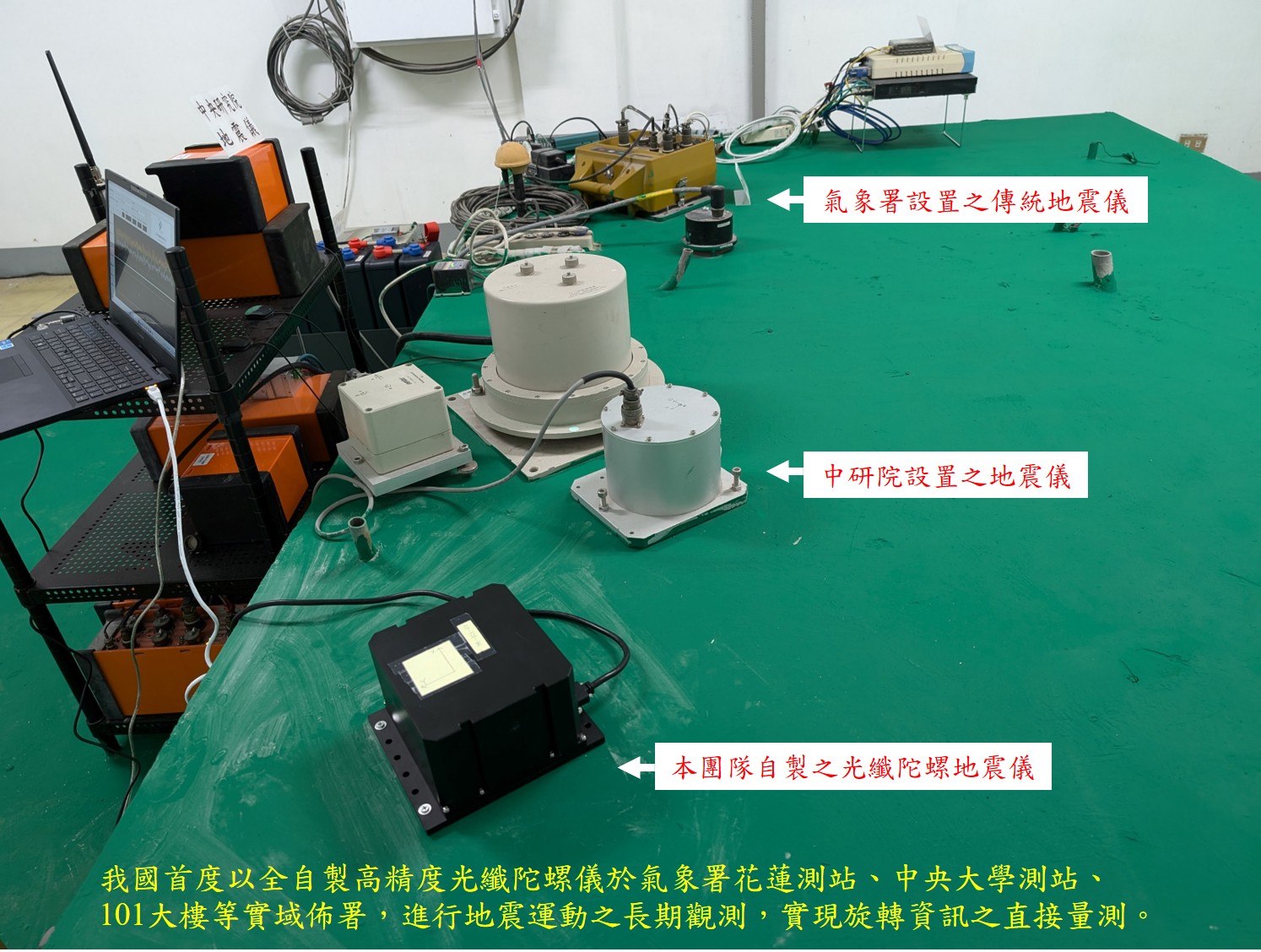

Fiber-Optic Gyroscope Seismometry- the last missing puzzle piece for high-precision multidimensional seismic sensing technology

Technology maturity:Others

Exhibiting purpose:Technology transactions

Trading preferences:Negotiate by self

*Organization

*Name

*Phone

*Main Purpose

*Discuss Further

*Job Category

*Overall Rating

*Favorite Area

*Key Tech Focus

*Willing to Receive Updates?

Other Suggestions

Coming soon!