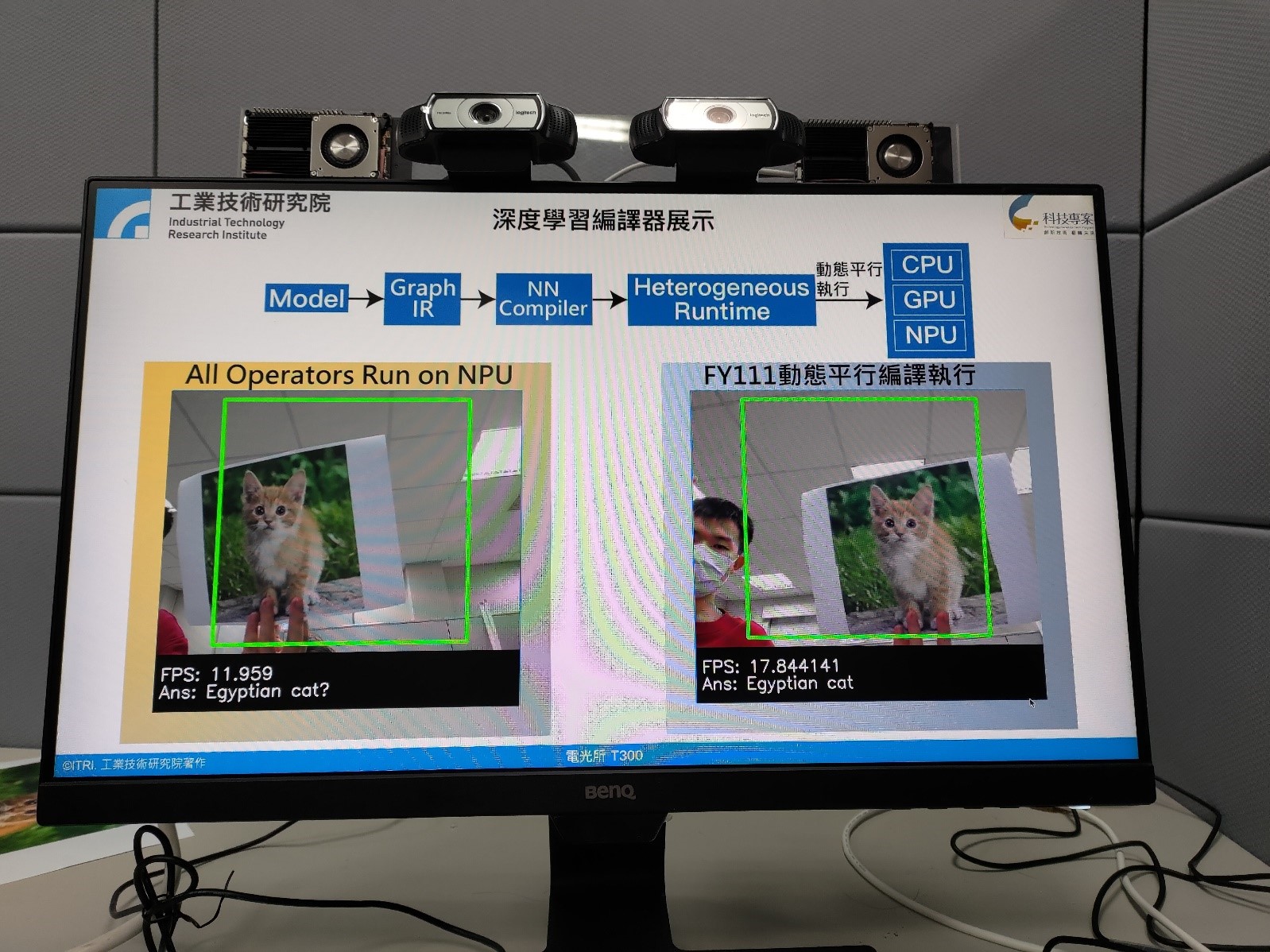

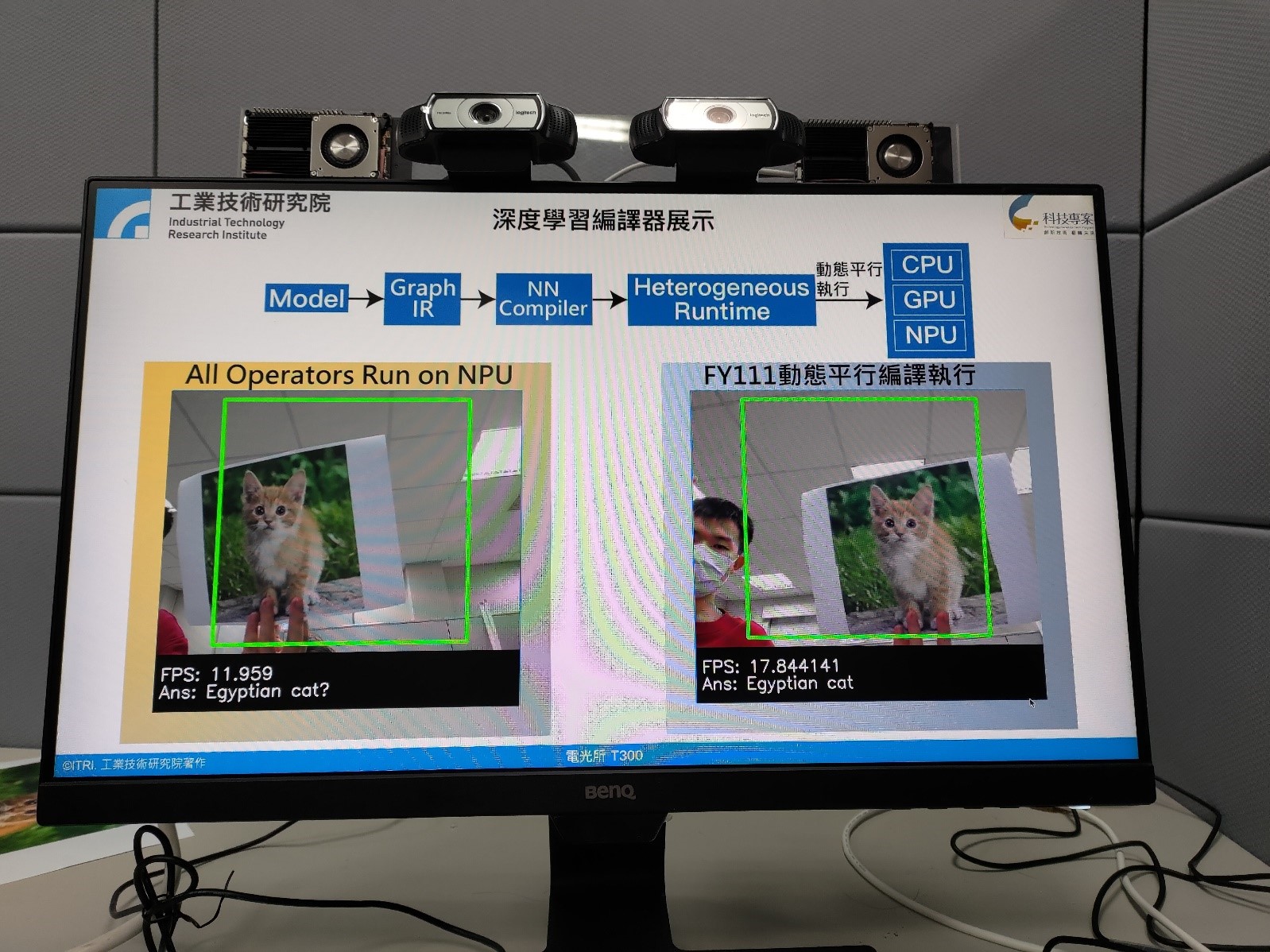

Neural Network Compiler for Parallel and Heterogeneous Inference on Multiple AI Accelerators

Deep Learning uses a complex structure of algorithms to run on AI hardware. Performance and Efficency are the major issues that need to be solved when enterprises introduce AI applications. The heterogeneous processor integrates DSP, GPU, NPU or ASIC into a heterogeneous AI SoC that provides cost-effective solution for AI application. ITRI develops dynamic parallel AI compiler and runtime techniques to compile AI model and to run AI operators in parallel on heterogeneous chips. This approach can improve computing performance and improve energy efficiency. This technology has been applied to commercially heterogeneous AI SoC (CPU+GPU+NPU), which can improve computing performance by more than 31.2% compared to all operators run on NPU accelerator.

[Technical Features]

•Provide the schedule optimization mechanisms for the heterogeneous AI SoC.

•Provide dynamic parallel compilation and runtime software environment for heterogeneous AI SoC.

•Provide dynamic load balance runtime to improve computing performance

ITRI is a world-leading applied technology research institute with more than 6,000 outstanding employees. Its mission is to drive industrial development, create economic value, and enhance social well-being through technology R&D. Founded in 1973, it pioneered in IC development and started to nurture new tech ventures and deliver its R&D results to industries. ITRI has set up and incubated companies such as TSMC, UMC, Taiwan Mask Corp., Epistar Corp., Mirle Automation Corp., and Taiwan Biomaterial Co.

Name:

Phone:03-5919111

Address:195, Sec. 4, Chung Hsing Rd., Chutung, Hsinchu, Taiwan 31040, R.O.C.

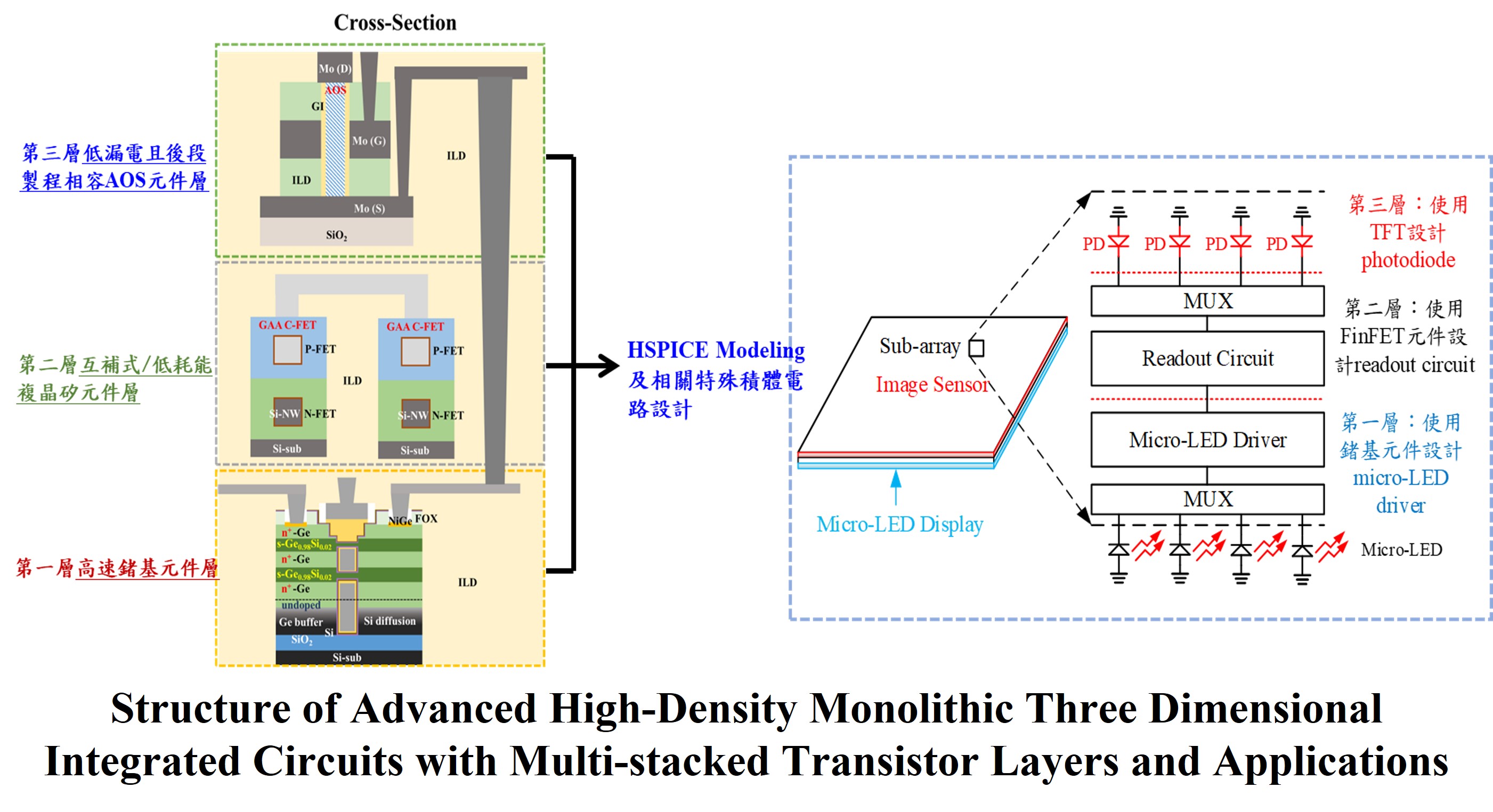

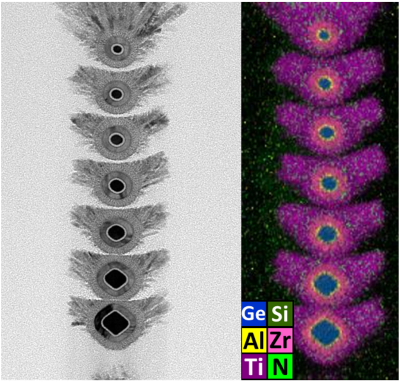

Development for Advanced High-Density Monolithic Three Dimensional Integrated Circuits with Multi-stacked Transistor Layers

High mobility materials, process, stacked channels, and thermal circuit simulation; Ferroelectric X:HfO2 for Negative Capacitance and POC(Proof-of-Concept) Applications; Atomic layer technologies for

Hybrid CMOS Inverter Comprised of Thin Film Transistors with Hetero-channel for Monolithic 3D-ICs and Ultra-high Resolution Flat-Panel Displays Applications

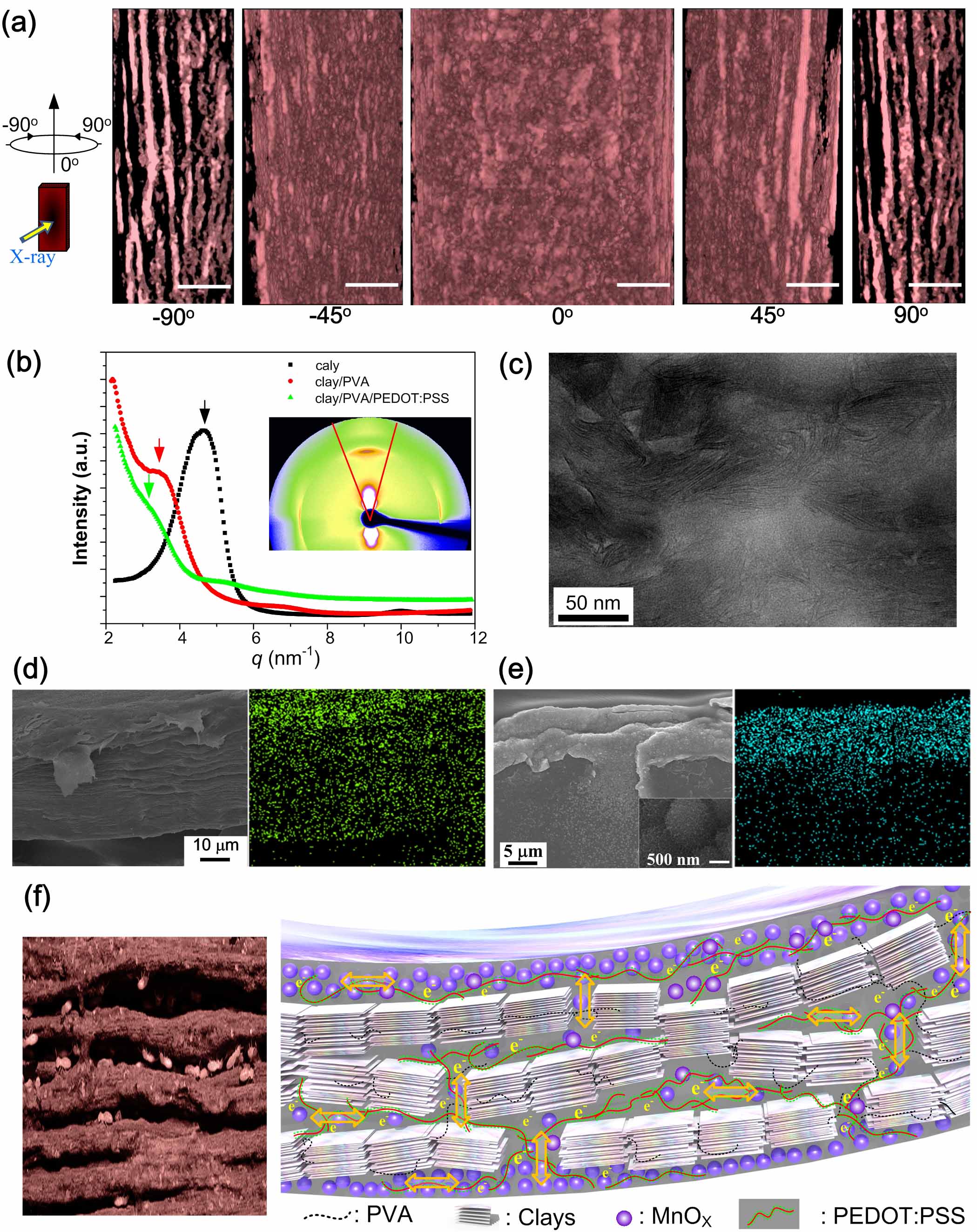

Next-generation energy for wearable device: bioinspired, eco-friendly, and felxible all-solid-state supercapacitors

Technology maturity:Prototype

Exhibiting purpose:Display of scientific results

Trading preferences:Negotiate by self

*Organization

*Name

*Phone

*Main Purpose

*Discuss Further

*Job Category

*Overall Rating

*Favorite Area

*Key Tech Focus

*Willing to Receive Updates?

Other Suggestions

Coming soon!