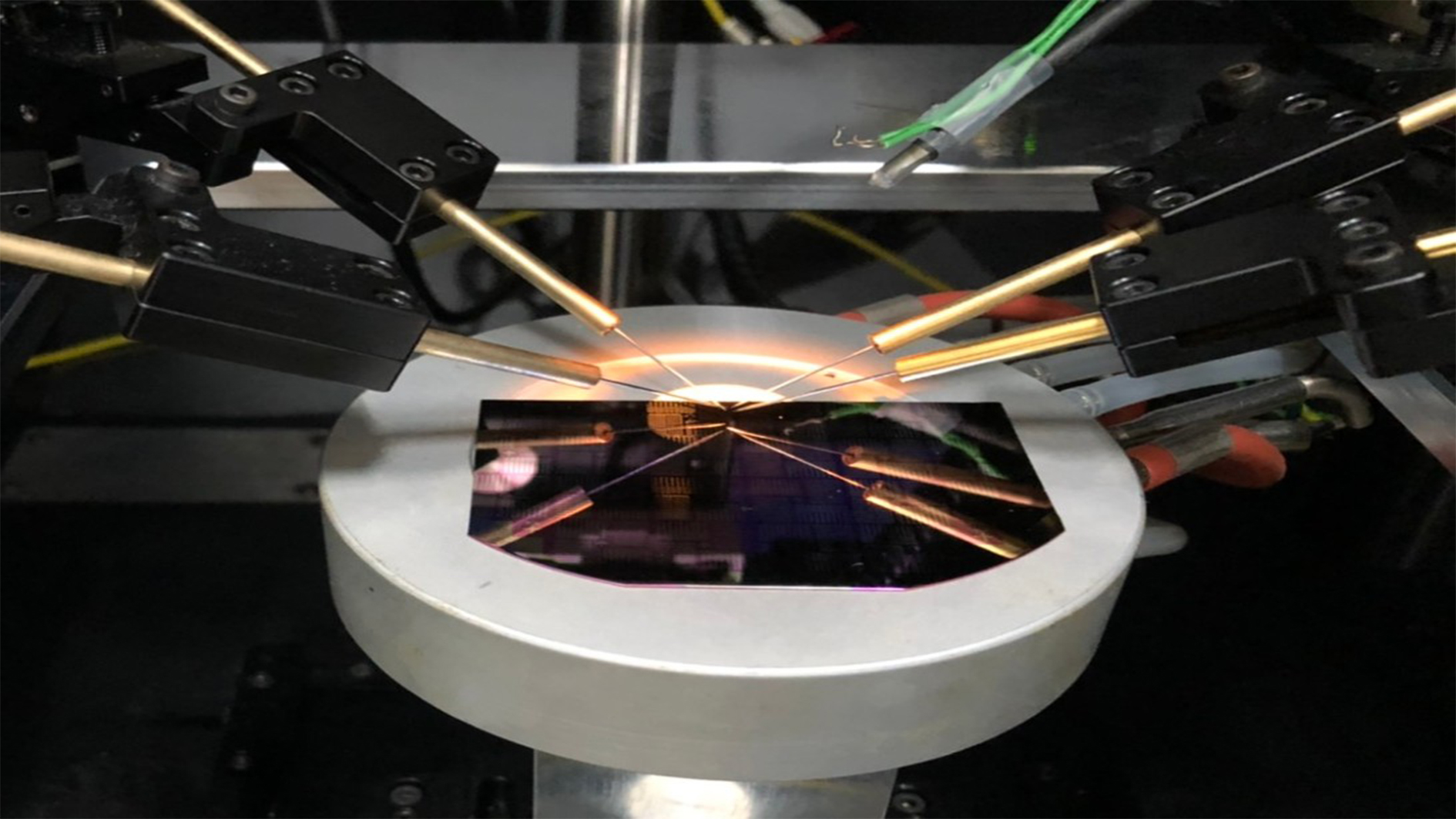

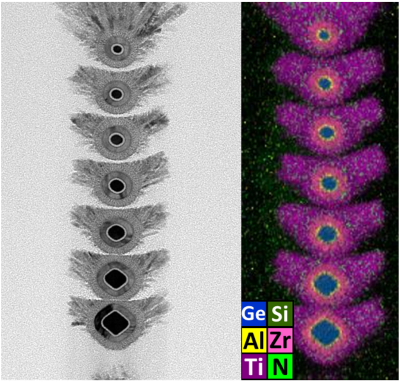

Low Temperature Polycrystalline Silicon Oxide (LTPO) TFT Architecture with Memory-embedded in Pixel for High-resolution and Power-saving Near-eye VR/AR Displays Applications

A novel LTPO-based display array technology with CBRAM-embedded in a pixel has been successfully developed for the high-resolution and power-saving near-eye VR/AR displays. And a high-voltage gain CMOS inverter comprised by LTPO architecture is demonstrated acting as a digital driving circuit for the realistic FPD applications.

In our work, a breakthrough in the bottleneck of N-channel AOS TFT performance has been made, such as high mobility of (>25cm2/V‧s), well on/off current ratio of (~10^9), and nearly ideal sub-threshold swing (S.S.~65mV/dec.). So that the novel LTPO transistors architecture with nonvolatile CBRAM-embedded in pixel can be pioneerly developed acting as the display switch/driving array, applicable for the next-generation high-resolution near-eye VR/AR displays. The technology features low operation voltage, less device footprint in a pixel, low signal propagation delay and low power consumption, which are demonstrated by a high-voltage gain LTPO-based inverter. With the additional integration of CBRAM in pixel to store image signal, the frame rate can be effectively lowered, resultantly decreasing power consumption. In conclusion, this technology is highly promising to meet the FPD industry’s needs for the next-generation high-resolution and power-saving VR/AR display electronics applications.

線上展網址:

https://tievirtual.twtm.com.tw/iframe/fd9e7945-5977-455c-8924-3271b572bee8?group=23bfb1fa-dd5b-4836-81a1-4a1809b1bae5&lang=en

National Yang Ming Chiao Tung University (NYCU) was formed in 2021 through the merger of National Yang Ming University and National Chiao Tung University. Located in Hsinchu, Taiwan, NYCU is a leading institution specializing in technology, engineering, medicine, and social sciences. The university is known for its strengths in research and innovation, particularly in areas such as information technology, biomedicine, and artificial intelligence. NYCU fosters interdisciplinary collaboration, global partnerships, and aims to nurture professionals with strong academic foundations and leadership skills to address societal challenges and contribute to technological advancements.

High mobility materials, process, stacked channels, and thermal circuit simulation; Ferroelectric X:HfO2 for Negative Capacitance and POC(Proof-of-Concept) Applications; Atomic layer technologies for

World-class ultra-precision optical processing technology and the non-contact floating display application

Hybrid CMOS Inverter Comprised of Thin Film Transistors with Hetero-channel for Monolithic 3D-ICs and Ultra-high Resolution Flat-Panel Displays Applications

Dual M-Layers Avalanche Photodiodes with High Single-Photon Detection Efficiency and High Saturation Output Power for Lidar applications

Technology maturity:Experiment stage

Exhibiting purpose:Technology transactions、Patent transactions

Trading preferences:Exclusive license/assignment、Technical license/cooperation、Negotiate by self

*Organization

*Name

*Phone

*Main Purpose

*Discuss Further

*Job Category

*Overall Rating

*Favorite Area

*Key Tech Focus

*Willing to Receive Updates?

Other Suggestions

Coming soon!