Energy-Efficient Optimization Problem Decision: Neural Network-based In-Memory Annealing Units for Route Scheduling and Genome Assembly

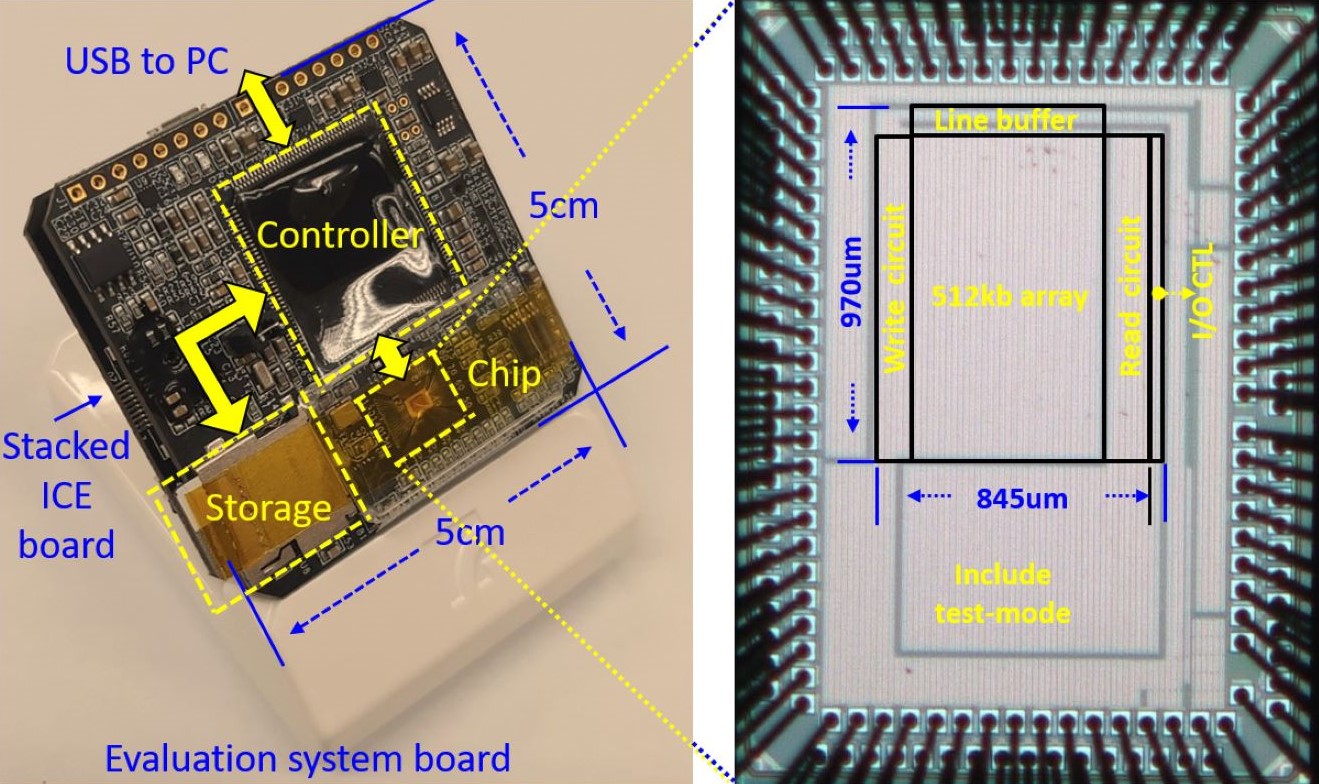

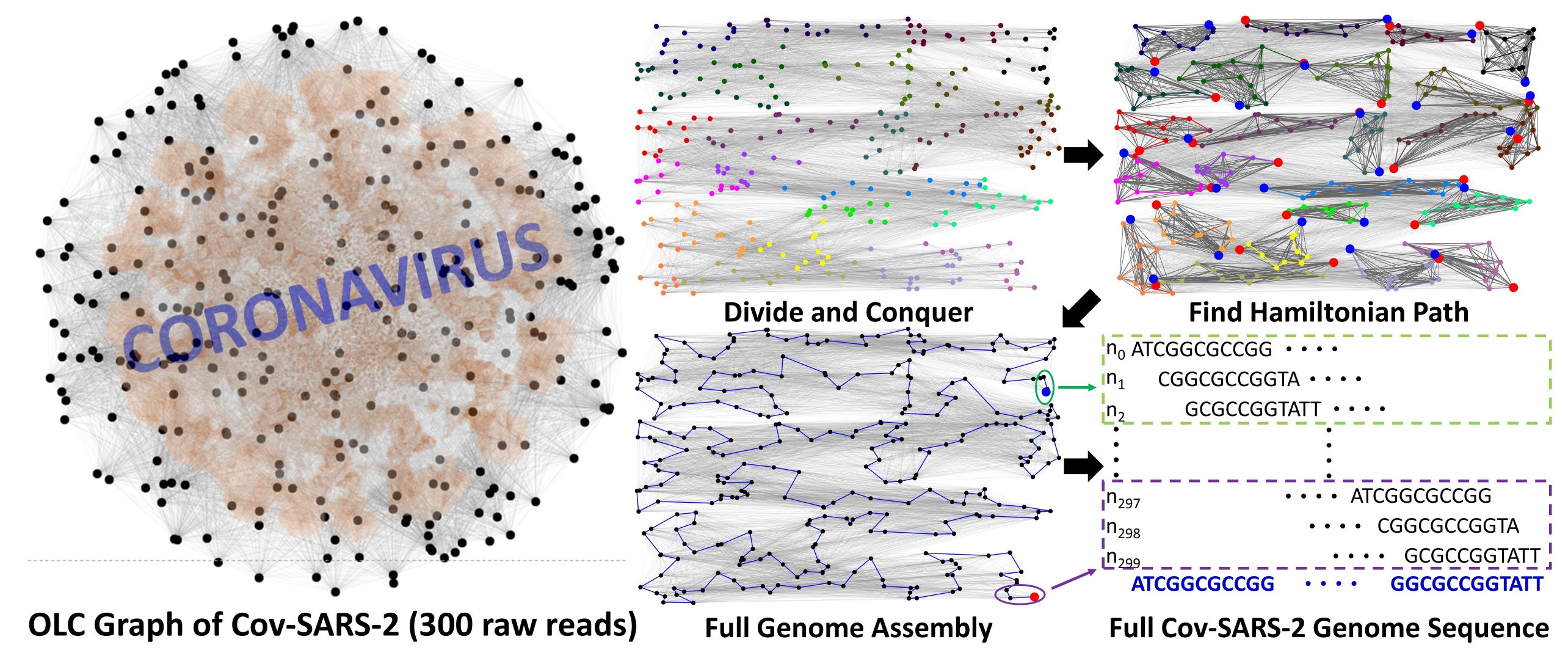

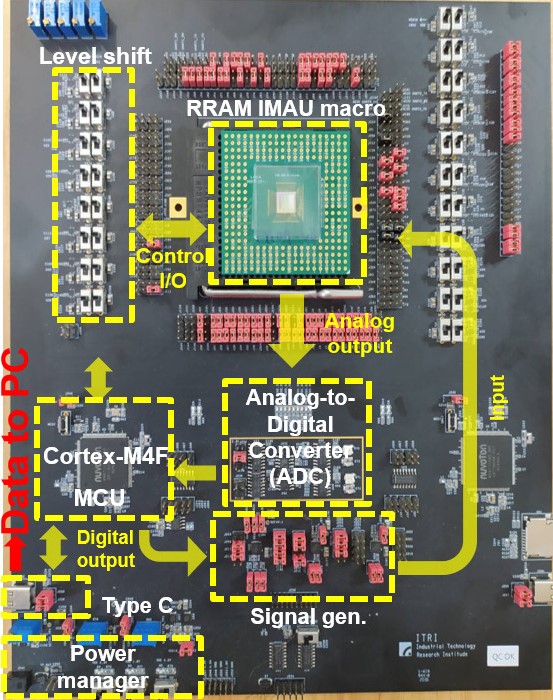

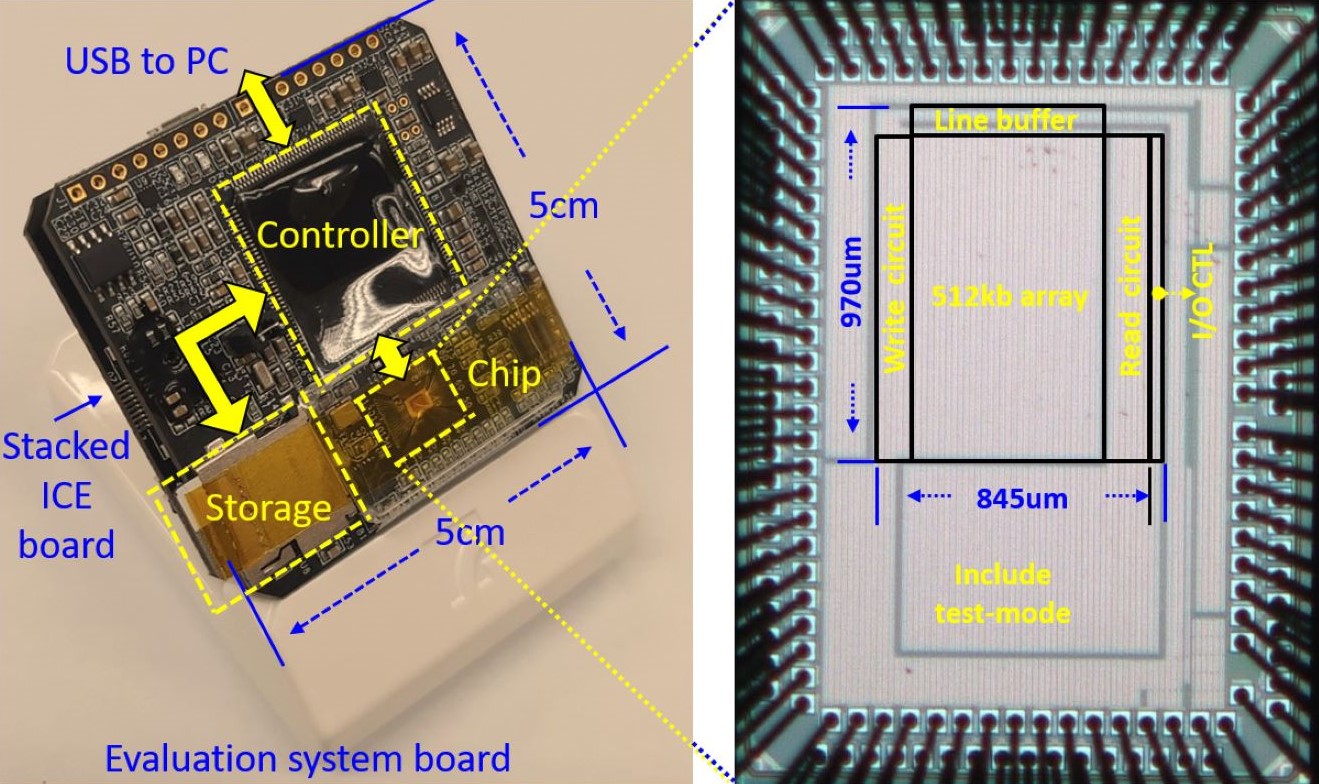

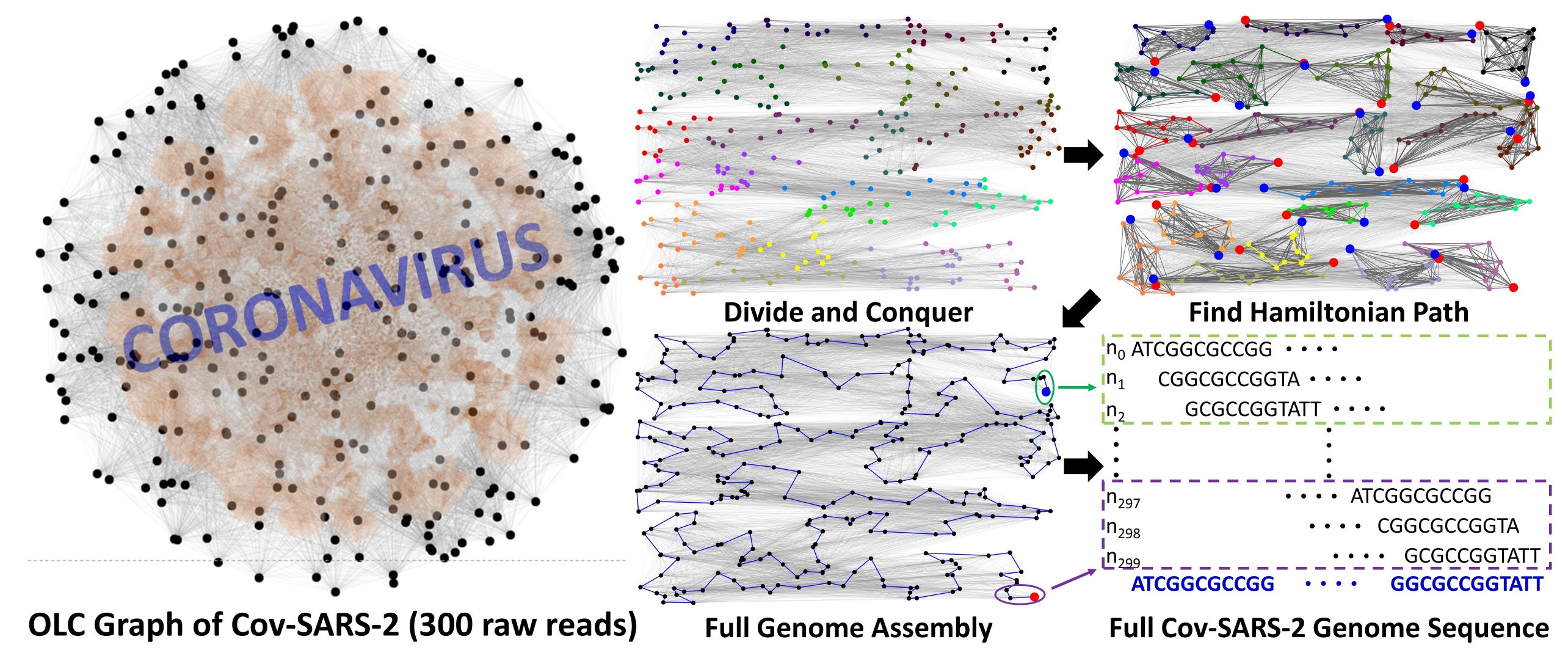

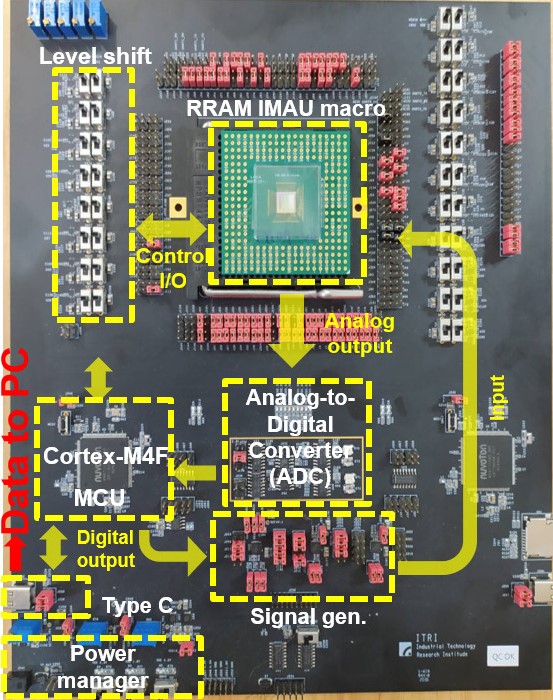

The technology combines memory devices, in-memory computing, and simulated annealing algorithms to create the world's first in-memory annealing unit (IMAU). First verified on 10-city traveling salesman problem and 300-read genome assembly, it is expected to be 1000 times faster than current hardware. It serves as a potential tool for high-speed optimal decision-making in chip design, biomedicine, and logistics, presented at IEDM 2021 and awarded first place in the 2024 Micron MIMORY Award.

National Yang Ming Chiao Tung University (NYCU) was formed in 2021 through the merger of National Yang Ming University and National Chiao Tung University. Located in Hsinchu, Taiwan, NYCU is a leading institution specializing in technology, engineering, medicine, and social sciences. The university is known for its strengths in research and innovation, particularly in areas such as information technology, biomedicine, and artificial intelligence. NYCU fosters interdisciplinary collaboration, global partnerships, and aims to nurture professionals with strong academic foundations and leadership skills to address societal challenges and contribute to technological advancements.

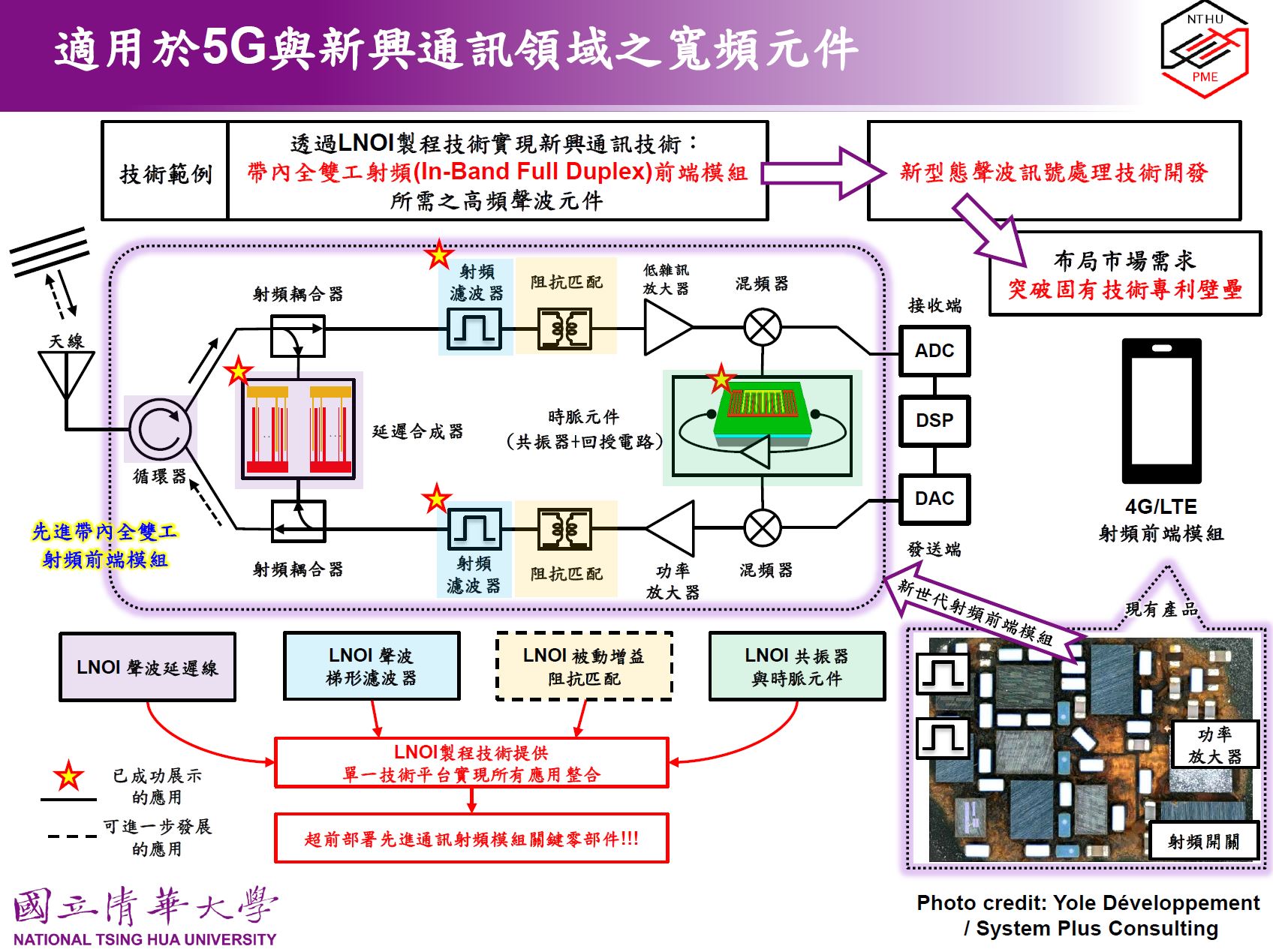

Next-generation wideband surface acoustic wave communication components based on thin-film lithium niobate on insulator technology

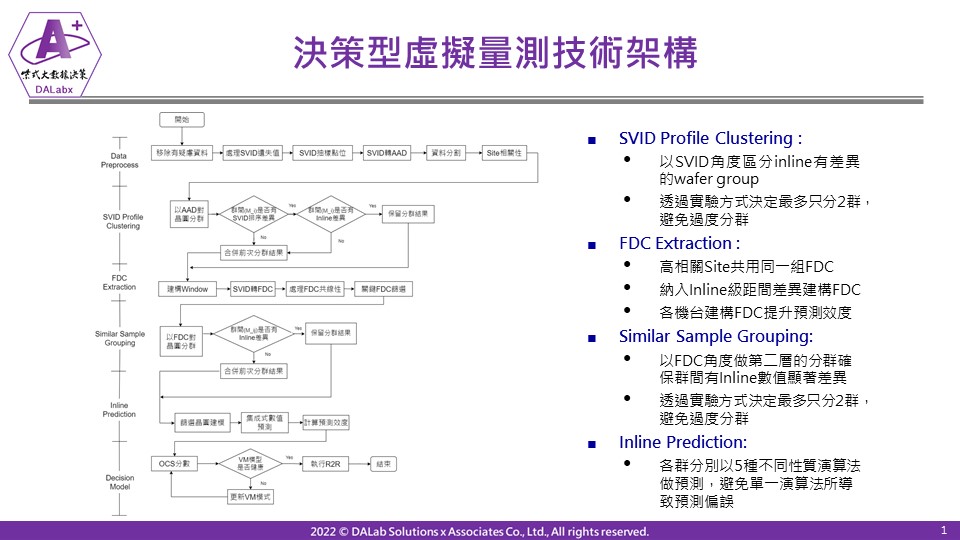

Optimizing Advanced Process Control Decision and Virtual Metrology Technology for Nano Technology Nodes for Semiconductor Manufacturing

Low Temperature Polycrystalline Silicon Oxide (LTPO) TFT Architecture with Memory-embedded in Pixel for High-resolution and Power-saving Near-eye VR/AR Displays Applications

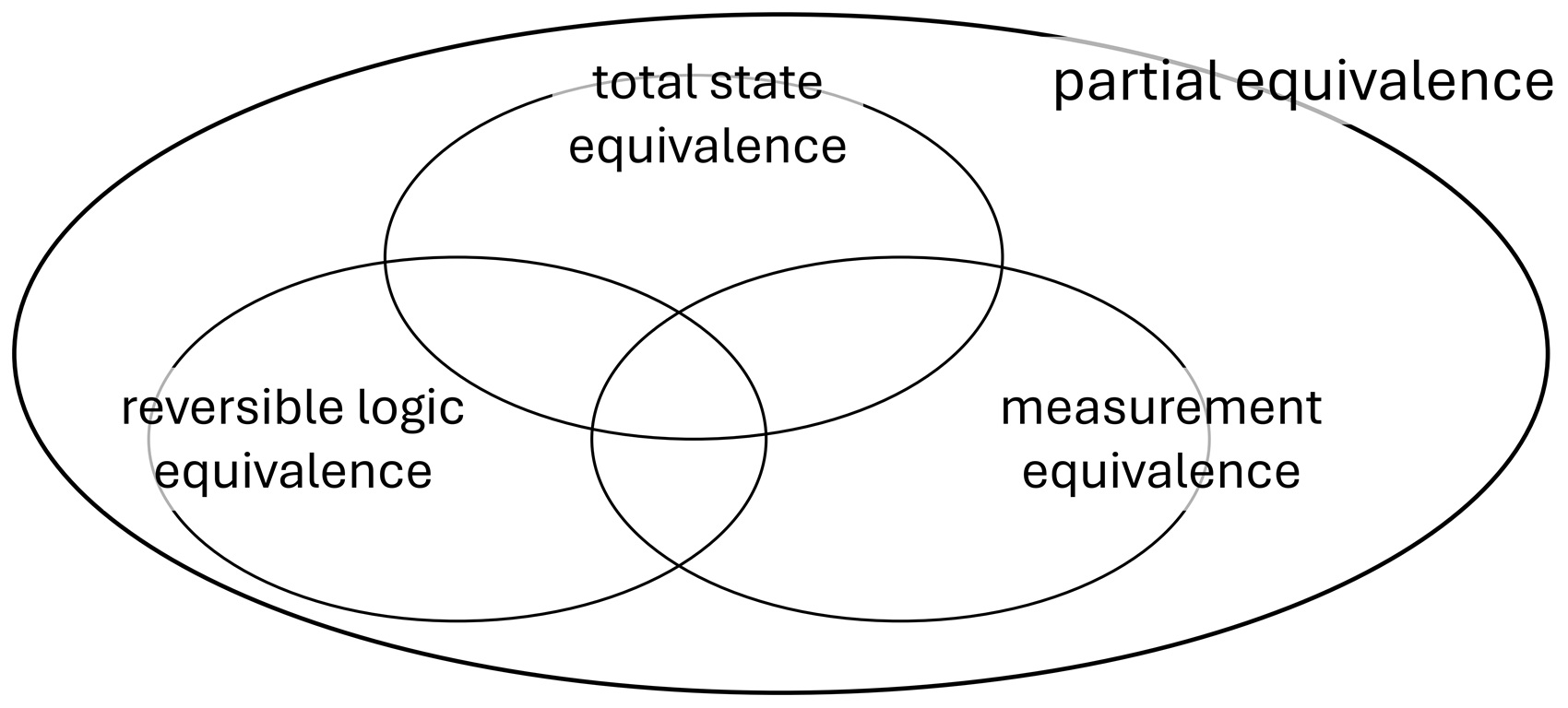

Quantum Circuit Verification: Static Partial Equivalence Checking and Dynamic Runtime Assertion Checking

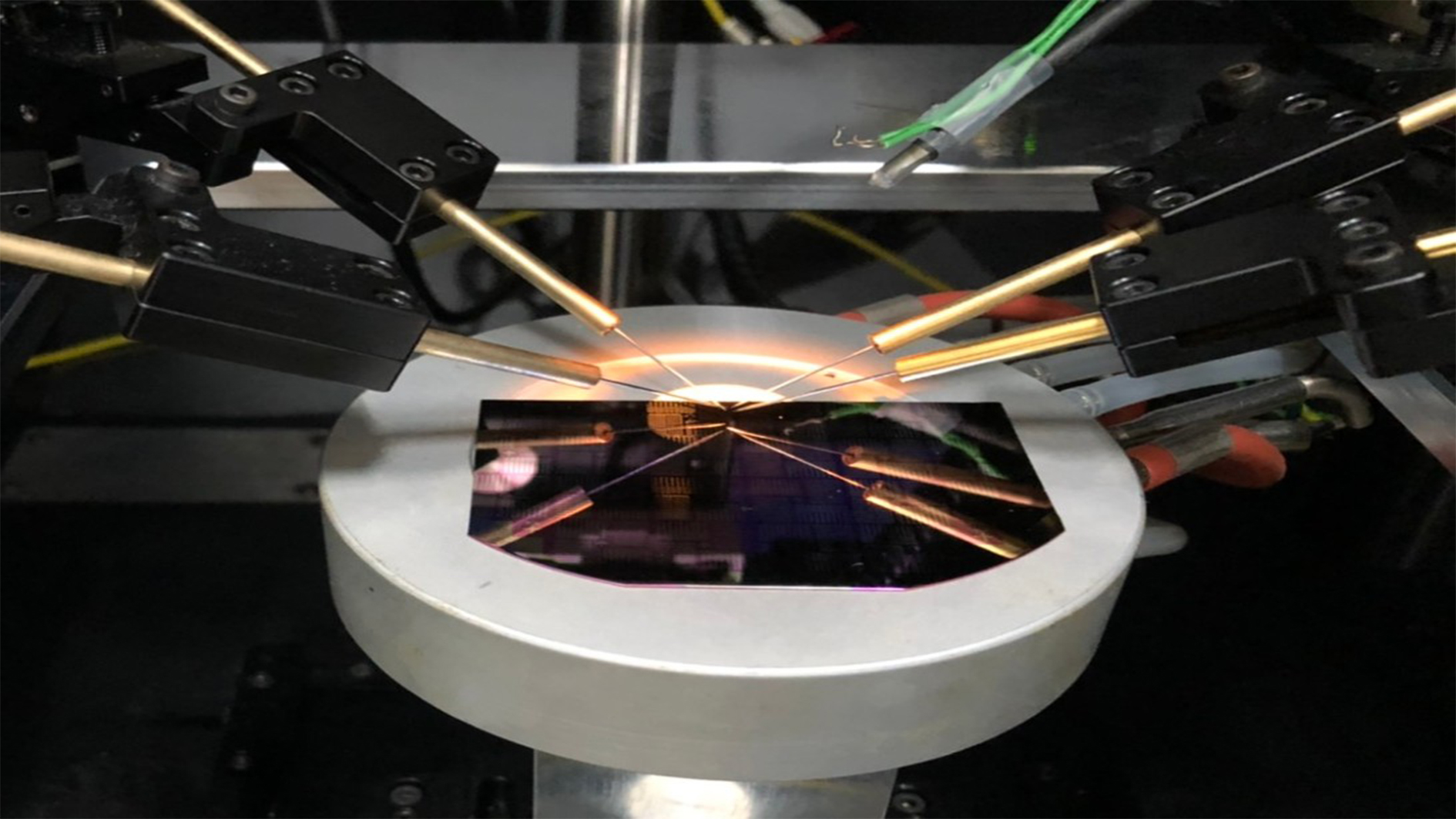

Technology maturity:Prototype

Exhibiting purpose:Display of scientific results

Trading preferences:Negotiate by self

*Organization

*Name

*Phone

*Main Purpose

*Discuss Further

*Job Category

*Overall Rating

*Favorite Area

*Key Tech Focus

*Willing to Receive Updates?

Other Suggestions

Coming soon!