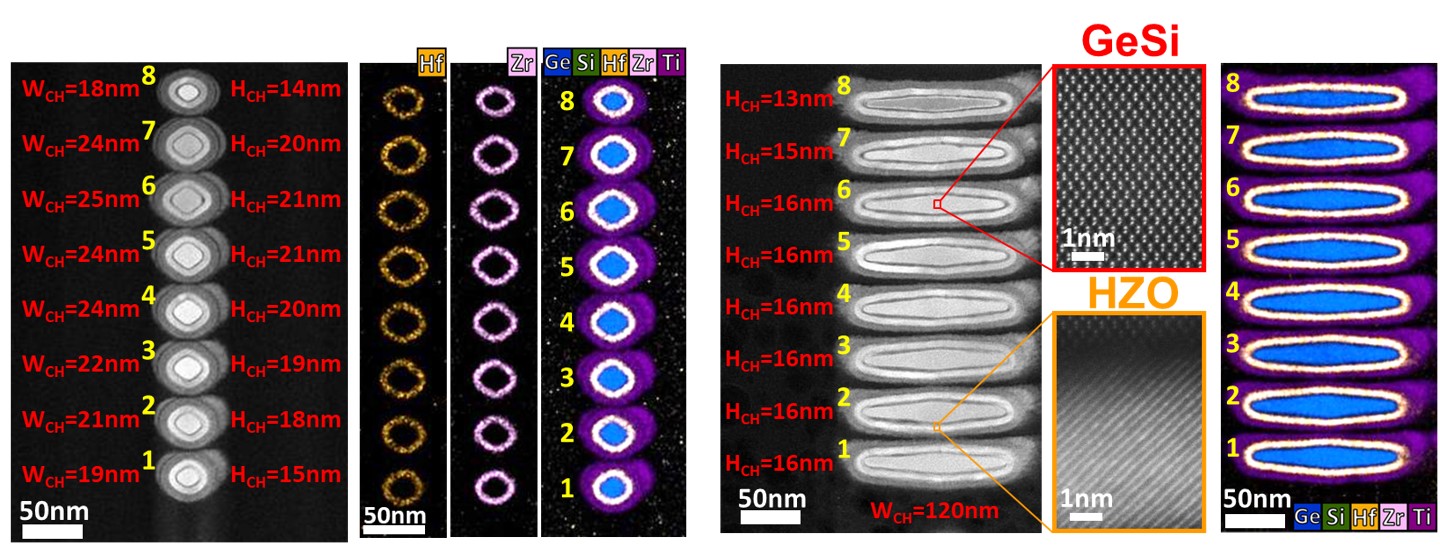

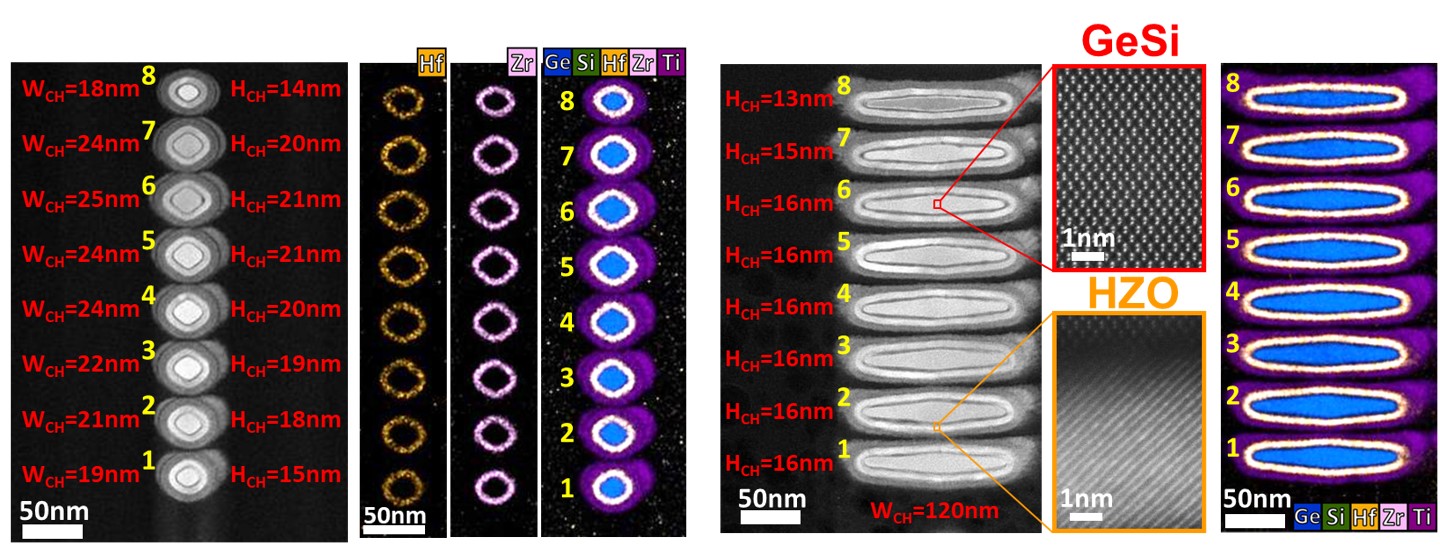

極高介電係數閘極堆疊整合於高層數堆疊通道電晶體:為了有效提升電晶體驅動電流,除了使用高遷移率通道及提升通道之堆疊層數,增加閘極堆疊中的介電層之介電係數也可以增加驅動電流。採用電漿輔助原層沉積HfxZryO2,通過優化Hf和Zr濃度以達到高介電係數,本團隊成功整合Hf0.2Zr0.8O2極高介電係數(k=47)介電層於八層堆疊鍺矽奈米線與奈米片電晶體,在VOV=VDS=0.5V,分別具有9200μA/μm per footprint與360μA per stack之紀錄驅動電流,透過模擬確認HZO在[Zr]=80%可擁有介電係數最大峰值,並使用模擬驗證極高介電係數閘極堆疊結合高層數堆疊通道能有效降低閘遲延。本研究成果已成功被國際頂級會議VLSI 2023所接受,足見此成果之重要性與傑出程度。堆疊式鍺矽奈米片閘極環繞式鐵電場效電晶體:鐵電場效應晶體管因具有CMOS製程之兼容性、簡單的單一電晶體之結構、低寫入能耗和非破壞性讀取之特性而在近期受到廣泛重視,尤其是在嵌入式非揮發性記憶體的應用上。本團隊成功開發出全世界第一個堆疊鍺矽閘極環繞式奈米片鐵電場效電晶體,具有低寫入電壓(2V)即可達到高記憶窗口(1.8V) ,可實現低功耗記憶體之應用,堆疊式奈米片結構達到高讀取電流,此成果具有高遲滯時間(1E4秒)可實現嵌入式非揮發性場效記憶體之應用,亦具有高反覆操作耐受力(>1E11 cycles)達到高可靠性,同時使用低製程溫(400oC)。本研究成果已成功被國際頂級會議VLSI 2023所接受,足見此成果之重要性與傑出程度。非晶相銦鎵鋅氧閘極環繞式奈米片場效電晶體:非晶相銦鎵鋅氧因具有低製程溫度、高電子遷移率與高均勻性而在近期受到廣泛重視,尤其是在單體3D堆疊上的應用。儘管a-IGZO之漏電流極低,其電子遷移率仍然無法與傳統四族材料媲美。閘極環繞式電晶體不僅可提升電流,更可進一步降低次臨界擺幅與漏電流。本團隊成功開發出全世界第一個非晶相銦鎵鋅氧閘極環繞式奈米片場效電晶體,並具有接近物理極限之SS (61 mV/dec)、極低漏電流(<1E7μA/um)、高Ion/Ioff (>1.3E8)、低DIBL(44mV/V)、正值門檻電壓及適用於CMOS之製程溫度300oC。本研究成果已成功被國際頂級會議VLSI 2023所接受,足見此成果之重要性與傑出程度。

臺大現有16個學院(含重點科技研究學院、創新設計學院、共同教育中心、國際學院、進修推廣學院),58個學系、146個研究所、34個碩博士學位學程,橫跨自然科學與人文社會藝術領域,每學期所開課程數近8,000 班,無論所擁有的學術領域或開設之課程數,在全國大學中均無出其右者,學生就讀於臺大,無疑是進入最為豐富的知識寶庫,可獲得最多元而優質的學習機會。

技術成熟度:實驗室階段

展示目的:研發成果展示

流通方式:自行洽談

*服務單位

*姓名

*電話

*您參觀這項展品的主要目的?

*您是否希望進一步洽談

*您的職務類別

*展覽整體評價

*最喜歡的展區

*期待展覽著重的技術領域

*是否願意收到電子報/最新資訊

其他建議

敬請期待!